UL集成逻辑门电路多余输入端的处理

发布时间:2013/10/17 20:46:00 访问次数:2841

对TTL集成逻辑门电路多余输入端的处理原则是:DF75AA160不改变原电路逻辑关系,保证电路能稳定可靠工作。

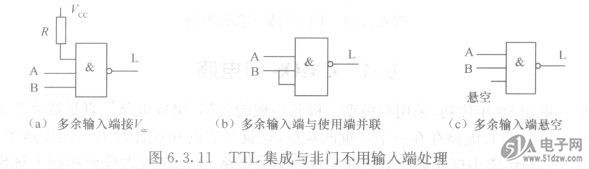

(1)与门、与非门不用的输入端应接高电平

具体方法是:

①将不用的输入端直接或经一个电阻R接电源Vcc,如图6.3.ll(a)所示。此方法采用最多。

②将不用的输入端与使用端并联,如图6.3. ll(b)所示。

③将不用的输入端悬空,如图6.3. ll(c)所示。对于TTL集成电路其输入端悬空相当于接高电平,即处于逻辑l状态。

(a)多余输入端接V (b)多余输入端与使用端并联 (c)多余输入端悬空

图6.3. 11 TTL集成与非门不用输入端处理

悬空的概念在以后各种数字器件或电路应用时常常会遇到,但必须指出:悬空的输入端易引入干扰,导致电路工作不可靠,因而这种方法仅适用于实验室。

另外,TTL集成电路其输入端与地之间外接不同的电阻时,表现为不同的电平。一般输入端外接电阻尺≥2kfl时,该输入端视为高电平;而输入端外接电阻R≤lOOc2时,该输入端视为低电平。

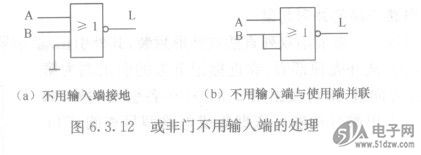

(2)或门、或菲门多余输入端应接低电平

具体方法是:

①将不用的输入端直接接地,如图6.3. 12(a)所示。

②将不用的输入端与使用端并联,如图6.3. 12(b)所示。最好采用前一种方法。

对TTL集成逻辑门电路多余输入端的处理原则是:DF75AA160不改变原电路逻辑关系,保证电路能稳定可靠工作。

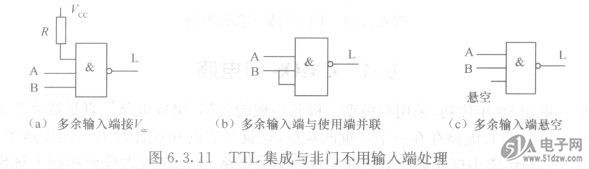

(1)与门、与非门不用的输入端应接高电平

具体方法是:

①将不用的输入端直接或经一个电阻R接电源Vcc,如图6.3.ll(a)所示。此方法采用最多。

②将不用的输入端与使用端并联,如图6.3. ll(b)所示。

③将不用的输入端悬空,如图6.3. ll(c)所示。对于TTL集成电路其输入端悬空相当于接高电平,即处于逻辑l状态。

(a)多余输入端接V (b)多余输入端与使用端并联 (c)多余输入端悬空

图6.3. 11 TTL集成与非门不用输入端处理

悬空的概念在以后各种数字器件或电路应用时常常会遇到,但必须指出:悬空的输入端易引入干扰,导致电路工作不可靠,因而这种方法仅适用于实验室。

另外,TTL集成电路其输入端与地之间外接不同的电阻时,表现为不同的电平。一般输入端外接电阻尺≥2kfl时,该输入端视为高电平;而输入端外接电阻R≤lOOc2时,该输入端视为低电平。

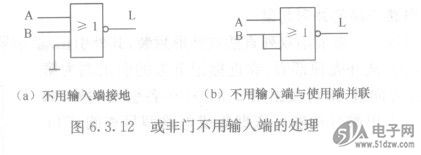

(2)或门、或菲门多余输入端应接低电平

具体方法是:

①将不用的输入端直接接地,如图6.3. 12(a)所示。

②将不用的输入端与使用端并联,如图6.3. 12(b)所示。最好采用前一种方法。

上一篇:TTL集成逻辑门的使用常识

公网安备44030402000607

公网安备44030402000607