同步十进制计数器74LS160(T4160)

发布时间:2013/10/20 11:52:36 访问次数:20501

同步十进制计数器74LS160(T4160)

同步十进制计数器74LS160(T4160)的引脚图、逻辑符号图,各引脚符号的含义及功能表与前面介绍的4位同步二进制计数器74LS161(T4161)类似(参见图8.3.7和表8.3.4),所不同的仅为741.S160的计数状态为0000~1001,完成十进制计数。每次计满10个时钟脉冲,从进位输出端输出进位脉冲,即CO= Q3 Qo S2 =1。

(3)同步十进制可逆计数器74LS192(T4192)

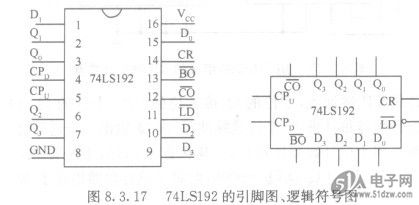

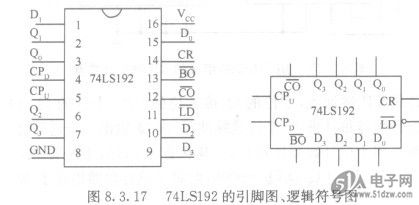

同步十进制可逆计数器74LS192 (T4192)的引脚图、逻辑符号图如图8.3.17所示。图中,Q3、Q2、Qi、Q0为计数器输出端;CPU、CPD分别为加法和减法计数脉冲输入端,上升沿触发计数;CR为复位(清零)端,高电平有效;I。D为置数端,低电平有效。

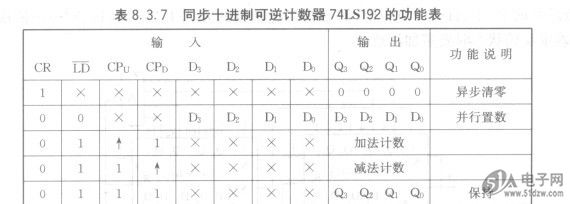

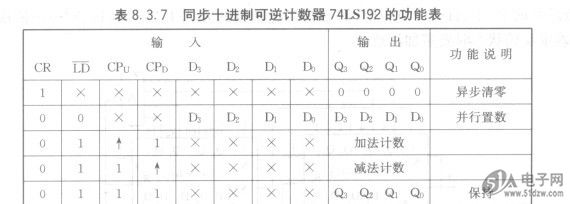

它的功能表如表8.3.7示,简要说明如下。

①异步预置并行数据。当LD为O,不管CPU、CPD为何种状态,可将预置数置入计数器(为异步置数),计数器输出Q3 Q2 Qi Qo=D3 D2 Di Do,

②异步清零。当CR为1时,不管CPU、CPD为何种状态,计数器输出Q3 Q2 Qi Qo =oooo。

③可逆计数。当计数脉冲CP加至CPu,CPD为1时,在CP上升沿作用下,计数器进行加法计数。当加法计数到状态为1001时,在CP下降沿,进位输出端CO产生一个负的进位脉冲,第10个CP的上升沿作用后,计数器复位。当计数脉冲CP加至CPD,CPu为1时,在CP上升沿作用下,计数器进行减法计数。同样,计数器进行减法计数时,设初态为1001,在第9个CP(CPD)上升沿作用下,计数器状态为0000,借位输出端BO产生一个负借位脉冲,第10个CP的上升沿作用后,计数器复位。

表8.3.7同步十进制可逆计数器74LS192的功能表

将74LS192进位输出端或借位输出端与后一级的脉冲输入端相连,可以实现多位计数器。

以上介绍了几种常用的集成计数器及其应用,它们的不同点主要表现在触发穷式、复位、预置,计数规律、码制等几方面,在应用中要注意。表8.3.8列出了部分常用的集成计数器。

同步十进制计数器74LS160(T4160)

同步十进制计数器74LS160(T4160)的引脚图、逻辑符号图,各引脚符号的含义及功能表与前面介绍的4位同步二进制计数器74LS161(T4161)类似(参见图8.3.7和表8.3.4),所不同的仅为741.S160的计数状态为0000~1001,完成十进制计数。每次计满10个时钟脉冲,从进位输出端输出进位脉冲,即CO= Q3 Qo S2 =1。

(3)同步十进制可逆计数器74LS192(T4192)

同步十进制可逆计数器74LS192 (T4192)的引脚图、逻辑符号图如图8.3.17所示。图中,Q3、Q2、Qi、Q0为计数器输出端;CPU、CPD分别为加法和减法计数脉冲输入端,上升沿触发计数;CR为复位(清零)端,高电平有效;I。D为置数端,低电平有效。

它的功能表如表8.3.7示,简要说明如下。

①异步预置并行数据。当LD为O,不管CPU、CPD为何种状态,可将预置数置入计数器(为异步置数),计数器输出Q3 Q2 Qi Qo=D3 D2 Di Do,

②异步清零。当CR为1时,不管CPU、CPD为何种状态,计数器输出Q3 Q2 Qi Qo =oooo。

③可逆计数。当计数脉冲CP加至CPu,CPD为1时,在CP上升沿作用下,计数器进行加法计数。当加法计数到状态为1001时,在CP下降沿,进位输出端CO产生一个负的进位脉冲,第10个CP的上升沿作用后,计数器复位。当计数脉冲CP加至CPD,CPu为1时,在CP上升沿作用下,计数器进行减法计数。同样,计数器进行减法计数时,设初态为1001,在第9个CP(CPD)上升沿作用下,计数器状态为0000,借位输出端BO产生一个负借位脉冲,第10个CP的上升沿作用后,计数器复位。

表8.3.7同步十进制可逆计数器74LS192的功能表

将74LS192进位输出端或借位输出端与后一级的脉冲输入端相连,可以实现多位计数器。

以上介绍了几种常用的集成计数器及其应用,它们的不同点主要表现在触发穷式、复位、预置,计数规律、码制等几方面,在应用中要注意。表8.3.8列出了部分常用的集成计数器。

上一篇:移位寄存器

公网安备44030402000607

公网安备44030402000607