栅源电压对导电沟道的影响

发布时间:2013/10/14 19:41:42 访问次数:9014

由图1.4.1(a)看出,NMOSFET的两个N+区被P型衬底隔开,XC2C64A-7VQ100I成为两个背靠背的PN结。在栅源电压VGS为零时,不管漏源电压VDs为何值,总有一个PN结是反向偏置的,因此漏极和源极之间不可能有电流流通。

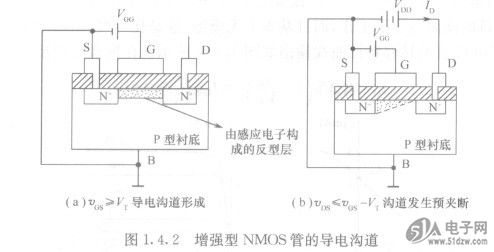

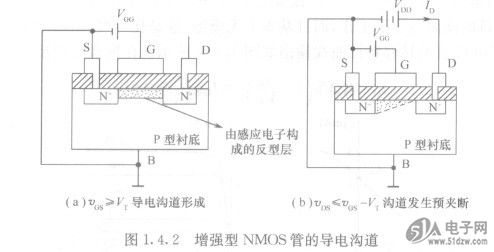

当把源极S和衬底B接地,并在栅、源极间加正电压GS,就会在栅极与衬底之间建立起一个垂直电场,其方向由栅极指向衬底,在此电场作用下,P型衬底中的少数载流子自由电子被吸引到栅极下面衬底的表层,形成一层以电子为多数载流子的N型薄层,这是一种能导电的薄层,它与P型衬底的类型相反,故称为反型层。反型层把源区和漏区连成一个整体,形成N型导电沟道,如图1.4.2(a)所示。VGS值越大,形成的导电沟道越宽,沟道电阻越小。这种在vcs一0时没有导电沟道,必须依靠栅源电压的作用才能形成导电沟道的FET称为增强型FET。图1.4.1(b)中所示的电路符号中,虚线即为沟道线,反映了增强型FET在vcs一0时沟道是断开的特点。

导电沟遒形成后,在漏极(D)和源极(S)之间加上正电压VDS,就会产生漏极电流iD。使D、S极之间开始导电的栅源电压称为开启电压,用VT表示。

由上述可见,MOS管的截止和导通是通过改变栅源电压VGS而实现的,所以MOS管是一种电压控制型导电器件;它在工作过程中只有一种极性的载流子参与导电,也称为单极型器件。

漏源电压对导电沟道的影响

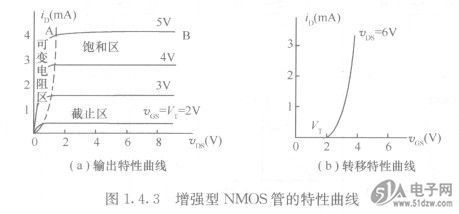

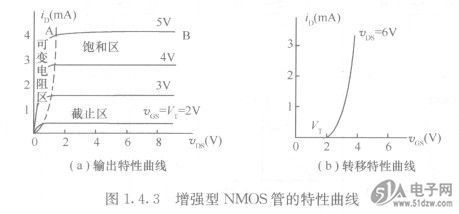

当VGS≥VT,外加较小的VDS时,漏极电流如将随VDS的上升迅速增大,在输出特性上如图1.4.3(a)所示的OA段,曲线斜率较大。但随着VDS的上升,由于沟道存在电位梯度,所以造成沟道厚度的不均匀,靠近源端厚,靠近漏端薄,即沟道呈楔形。当啦增大到一定数值,使得VGD=VGS- VDS= VT时,靠近漏端的反型层消失,沟道发生预夹断,如图1.4.2(b)所示。但耗尽区中仍有电流通过。VDS继续增加时,增加的部分主要降落在夹断区,沟道上的电压基本不变,所以VDS上升,iD趋于饱和,这时输出特性曲线斜率为0,如图1.4.3(a)所示的AB段。

由图1.4.1(a)看出,NMOSFET的两个N+区被P型衬底隔开,XC2C64A-7VQ100I成为两个背靠背的PN结。在栅源电压VGS为零时,不管漏源电压VDs为何值,总有一个PN结是反向偏置的,因此漏极和源极之间不可能有电流流通。

当把源极S和衬底B接地,并在栅、源极间加正电压GS,就会在栅极与衬底之间建立起一个垂直电场,其方向由栅极指向衬底,在此电场作用下,P型衬底中的少数载流子自由电子被吸引到栅极下面衬底的表层,形成一层以电子为多数载流子的N型薄层,这是一种能导电的薄层,它与P型衬底的类型相反,故称为反型层。反型层把源区和漏区连成一个整体,形成N型导电沟道,如图1.4.2(a)所示。VGS值越大,形成的导电沟道越宽,沟道电阻越小。这种在vcs一0时没有导电沟道,必须依靠栅源电压的作用才能形成导电沟道的FET称为增强型FET。图1.4.1(b)中所示的电路符号中,虚线即为沟道线,反映了增强型FET在vcs一0时沟道是断开的特点。

导电沟遒形成后,在漏极(D)和源极(S)之间加上正电压VDS,就会产生漏极电流iD。使D、S极之间开始导电的栅源电压称为开启电压,用VT表示。

由上述可见,MOS管的截止和导通是通过改变栅源电压VGS而实现的,所以MOS管是一种电压控制型导电器件;它在工作过程中只有一种极性的载流子参与导电,也称为单极型器件。

漏源电压对导电沟道的影响

当VGS≥VT,外加较小的VDS时,漏极电流如将随VDS的上升迅速增大,在输出特性上如图1.4.3(a)所示的OA段,曲线斜率较大。但随着VDS的上升,由于沟道存在电位梯度,所以造成沟道厚度的不均匀,靠近源端厚,靠近漏端薄,即沟道呈楔形。当啦增大到一定数值,使得VGD=VGS- VDS= VT时,靠近漏端的反型层消失,沟道发生预夹断,如图1.4.2(b)所示。但耗尽区中仍有电流通过。VDS继续增加时,增加的部分主要降落在夹断区,沟道上的电压基本不变,所以VDS上升,iD趋于饱和,这时输出特性曲线斜率为0,如图1.4.3(a)所示的AB段。

上一篇:场效应晶体管

上一篇:场效应管的特性与参数

公网安备44030402000607

公网安备44030402000607