晶振下方表层设置局部地平面

发布时间:2017/6/28 19:30:26 访问次数:598

【处理措施】

(1)晶振下方表层设置局部地平面,并通过THS4130IDR多个过孔与地层相连。

(2)将原来布在表层的时钟线,改为布在第三层(6层板)。

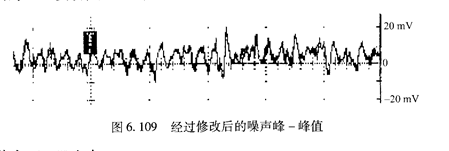

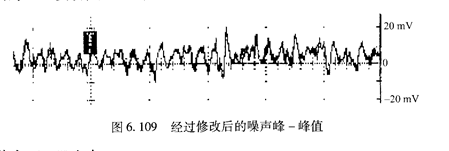

将修改后的PCB安装在产品中,再用上述简易近场探头测试,测得结果如图6.109所示。

【思考与启示】

(1)在多层板PCB设计中,建议在晶振下方设置局部地平面。对于两层板,此方法显 得更为重要。

(2)6层以上的多层板表层或底层不允许长距离布时钟线。最大允许的表层时钟线长度为时钟信号波长的1/20。

(3)晶振和驱动电路的下方及离这些电路300血l的距离内不能布信号线。

【处理措施】

(1)晶振下方表层设置局部地平面,并通过THS4130IDR多个过孔与地层相连。

(2)将原来布在表层的时钟线,改为布在第三层(6层板)。

将修改后的PCB安装在产品中,再用上述简易近场探头测试,测得结果如图6.109所示。

【思考与启示】

(1)在多层板PCB设计中,建议在晶振下方设置局部地平面。对于两层板,此方法显 得更为重要。

(2)6层以上的多层板表层或底层不允许长距离布时钟线。最大允许的表层时钟线长度为时钟信号波长的1/20。

(3)晶振和驱动电路的下方及离这些电路300血l的距离内不能布信号线。

上一篇:局部平面所在的区域不要布信号线

上一篇:接口电路布线与抗ESD干扰能力

热门点击

热门点击

- 二氧化硅的湿法刻蚀

- 钨的刻蚀

- 氮化硅的干法刻蚀

- 埋层的制备

- 芯片互连技术

- 两平行导线之间的距离对其寄生电容的影响

- 目前市场上出现的BGA封装,按基板的种类

- WLR――硅片级可靠性测试

- 电子束光刻胶

- 光刻工艺对掩模板的质量要求归纳

推荐技术资料

推荐技术资料

- 业余条件下PCM2702

- PGM2702采用SSOP28封装,引脚小而密,EP3... [详细]

公网安备44030402000607

公网安备44030402000607