内部噪声源

发布时间:2014/4/16 20:03:21 访问次数:543

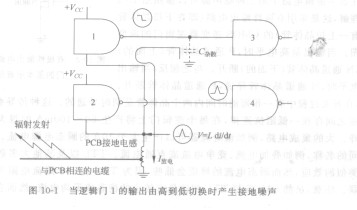

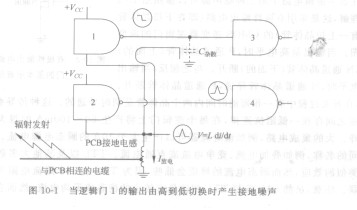

图10-1是一个由四个逻辑门组成的简单数字系统。考虑当逻辑门1的输出由高到低切换时会发生什么。CD4028BM96在逻辑门1切换之前,它的输出是高的,在逻辑门1和逻辑门2之间连线上的杂散电容被充电至电源电压。当逻辑门1切换时,在低电压被传输给逻辑门3之前,这些杂散电容必须放电。因此,很大的瞬态电流将流过接地系统以使这些杂散电容放电。由于接地电感,这个瞬态电流将在逻辑门1和逻辑门2的接地端产生噪声电压脉冲。如果逻辑门2的

输出是低的,这个噪声脉冲将被耦合至逻辑门4的输入端,如图10-1所示,这将导致逻辑门4切换产生信号完整性问题。

图10-1 当逻辑门1的输出由高到低切换时产生接地噪声

图10-1也表明与接地噪声有关的另一个问题,那就是电缆辐射。如图中所示,进出系统的电缆也是以电路的地为参考地,因此,一部分接地噪声电压将激发电缆作为天线进行辐射,进而产生EMC问题。导致EMC问题必需的噪声电压大约比产生信号完整性问题所需的噪声电压低三个数量级。降低接地噪声电压最实际的方法是降低接地系统的电感值。

从杂散电容通过逻辑门1输出端和接地导体形成的放电路径上包含有小的电阻。这形成一个可能产生振荡的高Q值串联谐振电路,且将导致逻辑门1的输出电压为负,如图10-2所示。

图10-1是一个由四个逻辑门组成的简单数字系统。考虑当逻辑门1的输出由高到低切换时会发生什么。CD4028BM96在逻辑门1切换之前,它的输出是高的,在逻辑门1和逻辑门2之间连线上的杂散电容被充电至电源电压。当逻辑门1切换时,在低电压被传输给逻辑门3之前,这些杂散电容必须放电。因此,很大的瞬态电流将流过接地系统以使这些杂散电容放电。由于接地电感,这个瞬态电流将在逻辑门1和逻辑门2的接地端产生噪声电压脉冲。如果逻辑门2的

输出是低的,这个噪声脉冲将被耦合至逻辑门4的输入端,如图10-1所示,这将导致逻辑门4切换产生信号完整性问题。

图10-1 当逻辑门1的输出由高到低切换时产生接地噪声

图10-1也表明与接地噪声有关的另一个问题,那就是电缆辐射。如图中所示,进出系统的电缆也是以电路的地为参考地,因此,一部分接地噪声电压将激发电缆作为天线进行辐射,进而产生EMC问题。导致EMC问题必需的噪声电压大约比产生信号完整性问题所需的噪声电压低三个数量级。降低接地噪声电压最实际的方法是降低接地系统的电感值。

从杂散电容通过逻辑门1输出端和接地导体形成的放电路径上包含有小的电阻。这形成一个可能产生振荡的高Q值串联谐振电路,且将导致逻辑门1的输出电压为负,如图10-2所示。

上一篇:频域和时域

上一篇:有极性输出毫话的CMOS逻辑门

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607