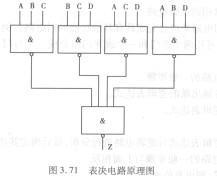

表决电路原理

发布时间:2014/1/27 11:17:48 访问次数:1703

由卡诺图得出逻辑表D2431P达式,并演化成“与非”的形式为

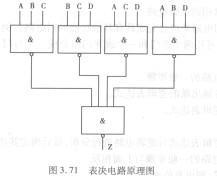

最后,画出用“与非门”构成的逻辑电路如图3. 71所示。

输入端接至逻辑开关(拨位开关)输出插口,输出端接逻辑电平显示端口,自拟真值表,逐次改变输入变量,验证逻辑功能。

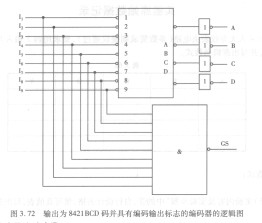

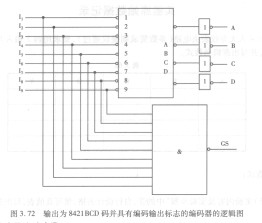

②试用10线一4线优先编码器74LS147(相关资料见实验六)和基本门电路构成输出为8421BCD码并具有编码输出标志的编码器。

逻辑图为:

如图3.72所示为输出为8421BCD码并具有编码输出标志的编码器的逻辑图。

由卡诺图得出逻辑表D2431P达式,并演化成“与非”的形式为

最后,画出用“与非门”构成的逻辑电路如图3. 71所示。

输入端接至逻辑开关(拨位开关)输出插口,输出端接逻辑电平显示端口,自拟真值表,逐次改变输入变量,验证逻辑功能。

②试用10线一4线优先编码器74LS147(相关资料见实验六)和基本门电路构成输出为8421BCD码并具有编码输出标志的编码器。

逻辑图为:

如图3.72所示为输出为8421BCD码并具有编码输出标志的编码器的逻辑图。

热门点击

热门点击

- 测试74LS151的逻辑功能

- 74LS248共阴极译码驱动器

- 晶体管损坏的一般原因

- 热敏电阻温度传感器的转换元件和转换电路

- 表决电路原理

- 8路模拟开关

- 在A/D转换器和D/A转换器的主要技术指标中

- 多功能数码闪字棒控制驱动电路原理图如何

- 555电路

- 交流毫伏表

推荐技术资料

推荐技术资料

- 业余条件下PCM2702

- PGM2702采用SSOP28封装,引脚小而密,EP3... [详细]

公网安备44030402000607

公网安备44030402000607