4位二进制加法器

发布时间:2013/10/18 20:58:17 访问次数:14670

一个全加器可实现两个1位二进制数的相加,B45196-05475-M309若将多个全加器作链式连接,即将低位的进位输出端与相邻高位的进位输入端相连,便能实现多位二进制数相加。图7.2.4所示为一个4位二进制加法器。图中,A3A2A1氏和B3 82 Bi 80为两个4位二进制数,每位相加的进位信号C3C2C1Co分别送给相邻高位作为输入信号。因此,任一位加法运算必须在其低位运算完

成之后才能进行,这种进位方式称为串行进位,故该加法器称为串行进位加法器。显然,它的运算速度较慢,为了克服这一缺点,可以采用超前进位加法器,其相关内容可参阅有关文献。

图7.2.4 4位二进制加法器

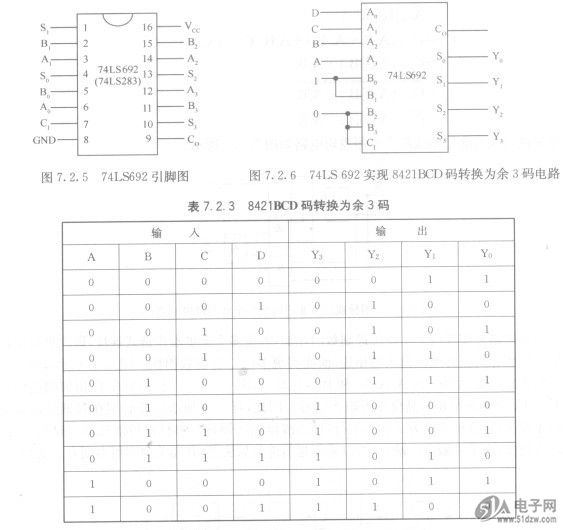

目前,全加器已制成集成电路,国产的74LS692兢是具有串行进位的4位加法器,其引脚排列图如图7.2.5所示。图中,A。A。A,氏和B。B2B.Bo为相加的两个4位二进制数输入端,S3S2S1So为其对应的和位输出端。C,为最低位的进位输入端,Co为最高位的进位输出端,主要用来扩展加法器的位数。VCc和GND分别为电源和接地端,使用非常方便。为了进一步提高加运算的速度,已有快速的四位超前进位加法器74LS283,它的功能、外引脚排列均与74LS692相同,可取而代之,运算速度可提高3.5倍以上。

全加器除了完成加法运算外,还可用在其他不同场合。

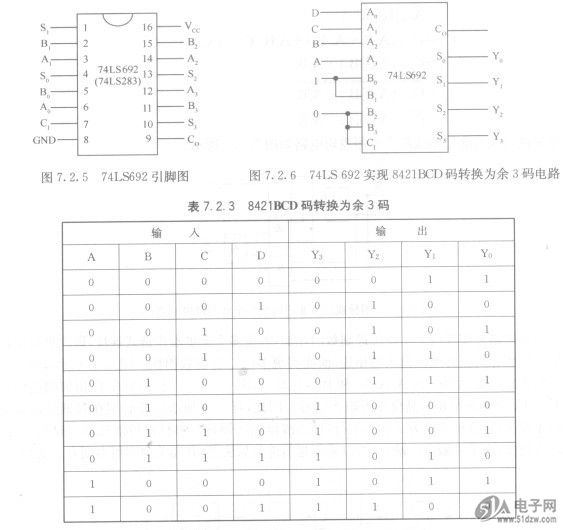

【例7.2.1】用74LS692设计码制转换电路,将8421BCD码转换为余3码。

解:设ABCD表示4位8421BCD码,Y3Y2Y1Yo表示4位余3码,根据两者的关系列出真值表如表7.2.3所示。 因此,用74LS692实现码制转换的电路,如图7.2.6所示。

一个全加器可实现两个1位二进制数的相加,B45196-05475-M309若将多个全加器作链式连接,即将低位的进位输出端与相邻高位的进位输入端相连,便能实现多位二进制数相加。图7.2.4所示为一个4位二进制加法器。图中,A3A2A1氏和B3 82 Bi 80为两个4位二进制数,每位相加的进位信号C3C2C1Co分别送给相邻高位作为输入信号。因此,任一位加法运算必须在其低位运算完

成之后才能进行,这种进位方式称为串行进位,故该加法器称为串行进位加法器。显然,它的运算速度较慢,为了克服这一缺点,可以采用超前进位加法器,其相关内容可参阅有关文献。

图7.2.4 4位二进制加法器

目前,全加器已制成集成电路,国产的74LS692兢是具有串行进位的4位加法器,其引脚排列图如图7.2.5所示。图中,A。A。A,氏和B。B2B.Bo为相加的两个4位二进制数输入端,S3S2S1So为其对应的和位输出端。C,为最低位的进位输入端,Co为最高位的进位输出端,主要用来扩展加法器的位数。VCc和GND分别为电源和接地端,使用非常方便。为了进一步提高加运算的速度,已有快速的四位超前进位加法器74LS283,它的功能、外引脚排列均与74LS692相同,可取而代之,运算速度可提高3.5倍以上。

全加器除了完成加法运算外,还可用在其他不同场合。

【例7.2.1】用74LS692设计码制转换电路,将8421BCD码转换为余3码。

解:设ABCD表示4位8421BCD码,Y3Y2Y1Yo表示4位余3码,根据两者的关系列出真值表如表7.2.3所示。 因此,用74LS692实现码制转换的电路,如图7.2.6所示。

上一篇:常用组合逻辑电路

上一篇:74LS138实现函数L电路

公网安备44030402000607

公网安备44030402000607