常用组合逻辑电路

发布时间:2013/10/18 20:48:55 访问次数:1124

在数字电路中,常需要对两个数进行加、减、乘、除算术运算,B45196-05156-M409目前这些运算在数字计算机中都是化作若干步加法运算进行的。因此,加法运算是最基本的运算。完成加法运算的逻辑电路称为加法器,加法器是构成算术运算器的基本单元。

加法器有半加器和全加器之分,如(1011)2+(0011)2中最低位1+1与次低位1+1的相加时有所不同,前者不考虑进位直接相加,我们称之为半加,实现半加的电路称为半加器;而后者除了本位的两个数相加外,还要考虑比它低的位的运算结果,即进位,通常称为全加,实现全加的电路为全加器。工程上大量使用的是全加器。

1.半加器

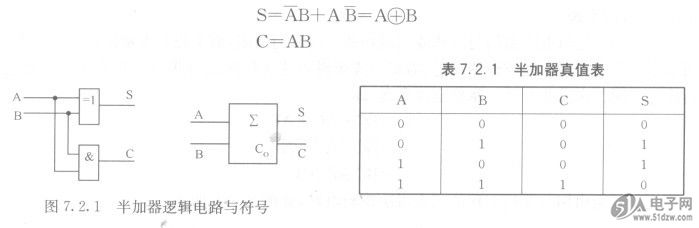

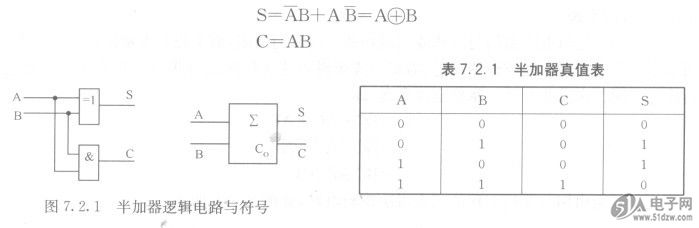

半加器逻辑电路与符号如图7.2.1所示。A和B表示两个二进制加数,S表示本位和,向高位的进位用C表示。半加器的真值表如表7.2.1所示,由电路或真值表可写出其逻辑表达式为

表7.2.1半加器真值表

图7.2.1半加器逻辑电路与符号

2.全加器

实际应用中往往都是多位二进制数的相加,需要用全加器。全加器的逻辑符号如图7.2.2所示。其中,Ai为被加数(/-0,1,2,…,n表示任意位,以下相同),B为加数,CH为来自相令B低位的进位数,Si为本位和,C:表示送往相邻高位的进位数。由二进制数相加规律可以列出全加器真值表,如表7.2.2所示。

图7.2.2全加器逻辑符号

在数字电路中,常需要对两个数进行加、减、乘、除算术运算,B45196-05156-M409目前这些运算在数字计算机中都是化作若干步加法运算进行的。因此,加法运算是最基本的运算。完成加法运算的逻辑电路称为加法器,加法器是构成算术运算器的基本单元。

加法器有半加器和全加器之分,如(1011)2+(0011)2中最低位1+1与次低位1+1的相加时有所不同,前者不考虑进位直接相加,我们称之为半加,实现半加的电路称为半加器;而后者除了本位的两个数相加外,还要考虑比它低的位的运算结果,即进位,通常称为全加,实现全加的电路为全加器。工程上大量使用的是全加器。

1.半加器

半加器逻辑电路与符号如图7.2.1所示。A和B表示两个二进制加数,S表示本位和,向高位的进位用C表示。半加器的真值表如表7.2.1所示,由电路或真值表可写出其逻辑表达式为

表7.2.1半加器真值表

图7.2.1半加器逻辑电路与符号

2.全加器

实际应用中往往都是多位二进制数的相加,需要用全加器。全加器的逻辑符号如图7.2.2所示。其中,Ai为被加数(/-0,1,2,…,n表示任意位,以下相同),B为加数,CH为来自相令B低位的进位数,Si为本位和,C:表示送往相邻高位的进位数。由二进制数相加规律可以列出全加器真值表,如表7.2.2所示。

图7.2.2全加器逻辑符号

公网安备44030402000607

公网安备44030402000607