可编程逻辑阵列(PLA)

发布时间:2013/10/21 19:57:39 访问次数:3755

从上面的分析,我们可知PROM的地址译码器采用全译码方式,行个地址码可选中2”个不同的存储单元,HA17901P且地址译码与存储单元有一一对应的关系。因此,即使有多个存储单元,所存放的内容完全相同,也必须重复存放,无法节省这些单元。从实现函数的角度看,PROM产生咒个变量的全部最小项完全没有必要。因此,PROM芯片的利用率不高。为解决此问题,在PROM的基础上出现了可编程逻辑阵列(PLA)。

(1)结构

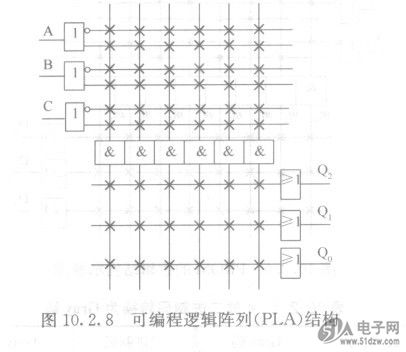

如图10.2.8所示。可编程逻辑阵列(PLA)与PROM类似,也是由与、或阵列构成。所不同的是,它的与阵列和或阵列一样是可编程的,n个输入变量产生的与项由编程决定。

图10.2.8可编程逻辑阵列(PLA)结构

(2)应用

用PLA进行组合逻辑设计时,一般应先将函数化简;然后根据简化的逻辑函数表达式确定与项的组合,再确定输出的编程。

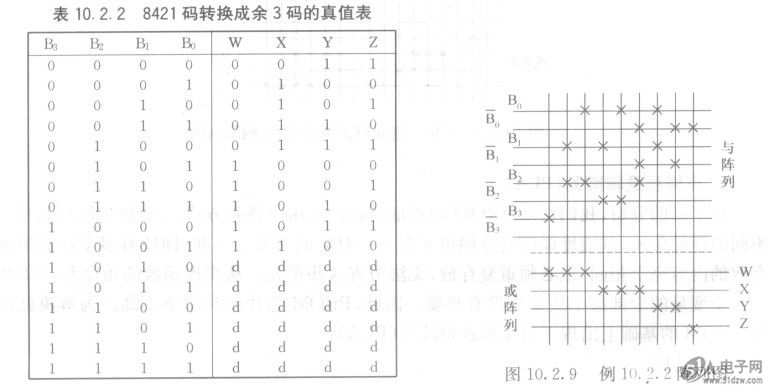

【例10.2.2】用PLA设计一个将8421码转换成余3码的代码转换电路。

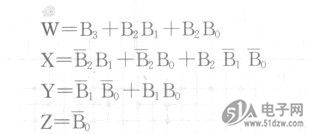

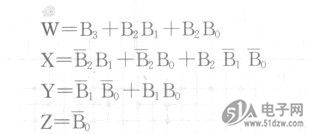

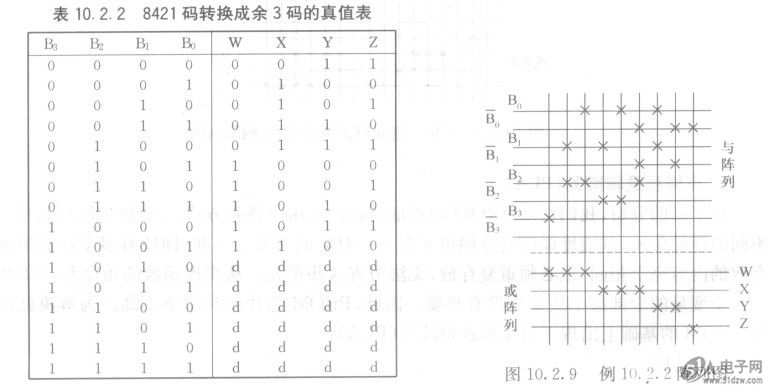

解设4位二进制码为B3、B2、B,、Bo,4位余3码为W、X、Y、Z,其对应关系如表10.2.2所示。将4位二进制码作为PLA的输入,余3码作为PLA的输出。根据表10.2.2可写出该电路的函数表达式,化简后得

可见,全部输出函数只包含9个不同的与项,所以该代码转换电路可用一个容量为4-9-4的PLA实现,其简化形式的阵列逻辑图(阵列图),如图10.2.9所示。

表10. 2.2 8421码转换成余3码的真值表

从上面的分析,我们可知PROM的地址译码器采用全译码方式,行个地址码可选中2”个不同的存储单元,HA17901P且地址译码与存储单元有一一对应的关系。因此,即使有多个存储单元,所存放的内容完全相同,也必须重复存放,无法节省这些单元。从实现函数的角度看,PROM产生咒个变量的全部最小项完全没有必要。因此,PROM芯片的利用率不高。为解决此问题,在PROM的基础上出现了可编程逻辑阵列(PLA)。

(1)结构

如图10.2.8所示。可编程逻辑阵列(PLA)与PROM类似,也是由与、或阵列构成。所不同的是,它的与阵列和或阵列一样是可编程的,n个输入变量产生的与项由编程决定。

图10.2.8可编程逻辑阵列(PLA)结构

(2)应用

用PLA进行组合逻辑设计时,一般应先将函数化简;然后根据简化的逻辑函数表达式确定与项的组合,再确定输出的编程。

【例10.2.2】用PLA设计一个将8421码转换成余3码的代码转换电路。

解设4位二进制码为B3、B2、B,、Bo,4位余3码为W、X、Y、Z,其对应关系如表10.2.2所示。将4位二进制码作为PLA的输入,余3码作为PLA的输出。根据表10.2.2可写出该电路的函数表达式,化简后得

可见,全部输出函数只包含9个不同的与项,所以该代码转换电路可用一个容量为4-9-4的PLA实现,其简化形式的阵列逻辑图(阵列图),如图10.2.9所示。

表10. 2.2 8421码转换成余3码的真值表

上一篇:常用PLD器件

上一篇:可编程阵列逻辑(PAL)

公网安备44030402000607

公网安备44030402000607