UY1105W-TR高电平翻转为低电平

发布时间:2019/10/24 12:27:16 访问次数:651

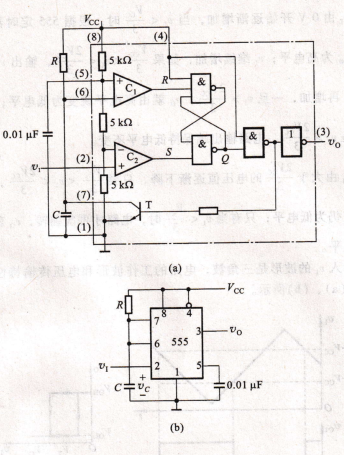

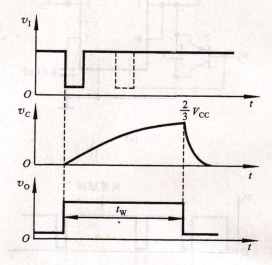

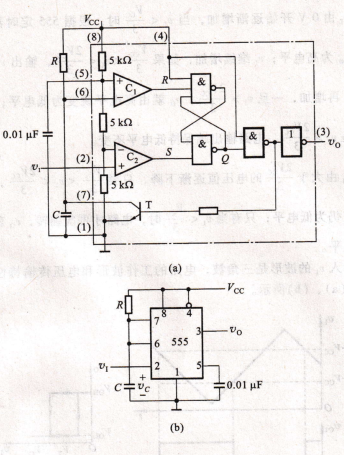

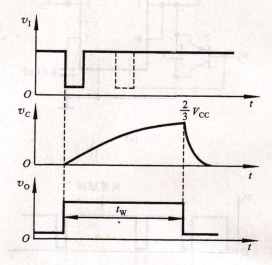

UY1105W-TR没有触发信号时ui处于高电平(u1>vcc/3),如果接通电源后0=0,v0=0,T导通,电容通过放电三极管T放电,使oc=0,v。保持低电平不变。如果接通电源后Q=1,放电三极管T就会截止,电源通过电阻R向电容C充电,当矽c上升到1严时,由于R=0,s=1,锁存器置0,v。为低电平。此时放电三极管T导通,电容C放电,v。保持低电平不变。因此,电路通电后在没有触发信号时,电路只有一种稳定状态v0=0。

若触发输入端施加触发信号(u1

择其来源。其中,全局输出使能控制信号有多个,不同型号的器件,其数量也不同(XC9500系列中r=4,MAX7000系列中r=6)。当oE为低电平时,I/0引脚可用作输入,引脚上的输入信号经过输入缓冲器送至内部可编程连线区。到其他I/o单元

D1和D2是钳位二极管,用于I/0引脚的保护。另外,通过编程可以使I/o引脚接上拉电阻或接地,也可以控制输出摆率(转换速率SR),选择快速方式可适应频率较高的信号输出,选择慢速方式则可减小功耗和降低噪声。ycclNT是器件内部逻辑电路的工作电压(也称为核心工作电压①),而ycc。的引入,可以使I/0引脚兼容多种电源系统。

CPLD编程简介,通过上一节的介绍可以看出,CPLD的各种逻辑功能的实现,都是由其内部的可编程单元控制的。这些单元大多采用E2PROM或闪烁存储器编程技术。编程过程就是将编程数据写入这些单元的过程。这一过程也称为下载(Down~load)或酉己置(Configure)。

写人CPLD中的编程数据都是由可编程器件的开发软件自动生成的。用户在开发软仵中输人设计及要求。利用开发软件对设计进行检查、分析和优化.

UY1105W-TR没有触发信号时ui处于高电平(u1>vcc/3),如果接通电源后0=0,v0=0,T导通,电容通过放电三极管T放电,使oc=0,v。保持低电平不变。如果接通电源后Q=1,放电三极管T就会截止,电源通过电阻R向电容C充电,当矽c上升到1严时,由于R=0,s=1,锁存器置0,v。为低电平。此时放电三极管T导通,电容C放电,v。保持低电平不变。因此,电路通电后在没有触发信号时,电路只有一种稳定状态v0=0。

若触发输入端施加触发信号(u1

择其来源。其中,全局输出使能控制信号有多个,不同型号的器件,其数量也不同(XC9500系列中r=4,MAX7000系列中r=6)。当oE为低电平时,I/0引脚可用作输入,引脚上的输入信号经过输入缓冲器送至内部可编程连线区。到其他I/o单元

D1和D2是钳位二极管,用于I/0引脚的保护。另外,通过编程可以使I/o引脚接上拉电阻或接地,也可以控制输出摆率(转换速率SR),选择快速方式可适应频率较高的信号输出,选择慢速方式则可减小功耗和降低噪声。ycclNT是器件内部逻辑电路的工作电压(也称为核心工作电压①),而ycc。的引入,可以使I/0引脚兼容多种电源系统。

CPLD编程简介,通过上一节的介绍可以看出,CPLD的各种逻辑功能的实现,都是由其内部的可编程单元控制的。这些单元大多采用E2PROM或闪烁存储器编程技术。编程过程就是将编程数据写入这些单元的过程。这一过程也称为下载(Down~load)或酉己置(Configure)。

写人CPLD中的编程数据都是由可编程器件的开发软件自动生成的。用户在开发软仵中输人设计及要求。利用开发软件对设计进行检查、分析和优化.

公网安备44030402000607

公网安备44030402000607