TNETW5306PYP 失落脉冲检测

发布时间:2019/10/24 12:26:54 访问次数:1008

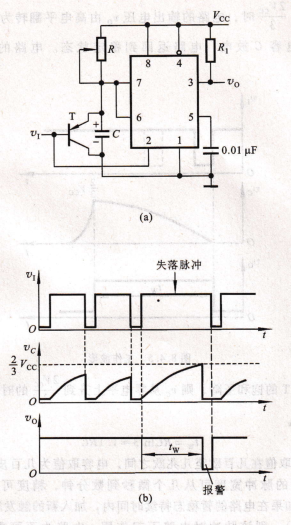

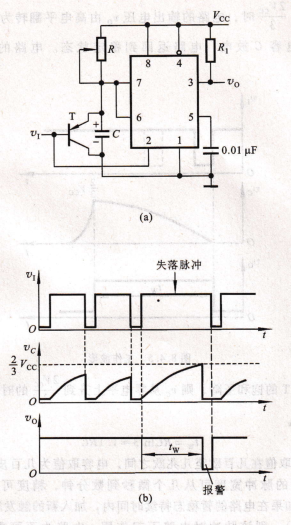

TNETW5306PYP如果忽略T的饱和压降。则vc从零电平上升到2vcc/3的时间 ,即为输出电压v0 的脉宽tw

tw=RCln3≈ 1.1RC (8.4.1)

通常R的取值在几百欧至几兆欧之间,电容取值为几百皮法到几百微法。这种电路产生的脉冲宽度可从几个微秒到数分钟,精度可达0.1%。由图8.4.5可知,如果在电路的暂稳态持续时间内,加人新的触发脉冲(如图8.4.5中的虚线所示),则该脉冲对电路不起作用,电路为不可重复触发单稳触发器。

由555定时器构成的可重复触发单稳电路如图8.4,6所示。当o1输人负向脉冲后,电路进人暂稳态,同时三极管T导通,电容C放电。输人负脉冲撤除后,电容C充电,在oc未充到飞产之前,电路处于暂稳态。如果在此期间,又加人新的触发脉冲,三极管T又导通,电容C再次放电,输出仍然维持在暂稳态。只有在触发脉冲撤除后且在输出脉宽Jw时间内没有新的触发脉冲,电路才返回到稳定状态。该电路可用作失落脉冲检测,或对电机转速或人体的心律进行监视,如果转速不稳或人体的心律不齐时,v0的低电平可用作报警信号。

如果将单稳态电路的电压控制端加人一个变化电压,当控制电压升高时,电路的阈值电压升高,输出的脉冲宽度随之增加;而当控制电压降低时,电路的阈值电压也降低,单稳的输出脉宽则随之减小。如果加入的控制电压是如图8.4.7(b)所示的三角波,则在单稳的输出端便可得到一串随控制电压变化的脉宽调制波形。

并自动对逻辑电路进行划分、布局和布线,然后按照一定的格式生成编程数据

文件,再通过编程电缆将编程数据写人CPLD中。有关可编程器件的开发过程

可以参阅附录C。

目前,绝大部分CPLD器件具有ISP功能。例如,Akn公司的MAX7000S(5V)、 MAX7000A(3..3Ⅴ)和MAX7000B(2.5Ⅴ)系歹刂, Xilinx公司的XC9500系列以及Lathce公司的CPLD器件等。ISP器件的编程必须具各三个条件:ISP专用编程电缆、微机、ISP编程软件。编程时,用户首先将ISP编程电缆的一端接到微机的数据传输端口上①,另一端接到电路板上被编程器件的ISP接口上,然后通过编程软件发出编程命令,将编程数据传送到芯片中。

ISP接口也不完全相同,但基本上都支持中都设有JTAG规定的4个I/0引脚。各引脚.

TDO的数据可以用于编程校验,也可以作为多个CPLD串行编程时下一个CPLD器件的输入数据,如图7,3,7所示。多数CPLD的这4个编程引脚也可以作为用户I/0使用。

与后面将要介绍的FPGA相比,尽管CPLD在电路规模和灵活性方面不如FPGA,但是它的可加密性和传输延时预知性,使得CPLD仍广泛应用于数字系统设计中。

目前,各大生产厂商仍不断开发出集成度更高、速度更快(功耗更低的CPLD新产品,核心工作电源可以低到1.8V。表7.3.2所示为几种典型的CPLD产品。

可以是并口、串口或USB口,视编程软件所支持的端口而定。

系Joint Test Action Group的缩写,指由该组织制定的IEEE 1149,l接口标准。现场可编程门阵列(FPGA①)是⒛世纪80年代中期发展起来的另一种类型的可编程器件。它不像CPLD那样采用可编程的“与一或”阵列来实现逻辑函数,

系Field Programmable Gate Array的缩写。

TNETW5306PYP如果忽略T的饱和压降。则vc从零电平上升到2vcc/3的时间 ,即为输出电压v0 的脉宽tw

tw=RCln3≈ 1.1RC (8.4.1)

通常R的取值在几百欧至几兆欧之间,电容取值为几百皮法到几百微法。这种电路产生的脉冲宽度可从几个微秒到数分钟,精度可达0.1%。由图8.4.5可知,如果在电路的暂稳态持续时间内,加人新的触发脉冲(如图8.4.5中的虚线所示),则该脉冲对电路不起作用,电路为不可重复触发单稳触发器。

由555定时器构成的可重复触发单稳电路如图8.4,6所示。当o1输人负向脉冲后,电路进人暂稳态,同时三极管T导通,电容C放电。输人负脉冲撤除后,电容C充电,在oc未充到飞产之前,电路处于暂稳态。如果在此期间,又加人新的触发脉冲,三极管T又导通,电容C再次放电,输出仍然维持在暂稳态。只有在触发脉冲撤除后且在输出脉宽Jw时间内没有新的触发脉冲,电路才返回到稳定状态。该电路可用作失落脉冲检测,或对电机转速或人体的心律进行监视,如果转速不稳或人体的心律不齐时,v0的低电平可用作报警信号。

如果将单稳态电路的电压控制端加人一个变化电压,当控制电压升高时,电路的阈值电压升高,输出的脉冲宽度随之增加;而当控制电压降低时,电路的阈值电压也降低,单稳的输出脉宽则随之减小。如果加入的控制电压是如图8.4.7(b)所示的三角波,则在单稳的输出端便可得到一串随控制电压变化的脉宽调制波形。

并自动对逻辑电路进行划分、布局和布线,然后按照一定的格式生成编程数据

文件,再通过编程电缆将编程数据写人CPLD中。有关可编程器件的开发过程

可以参阅附录C。

目前,绝大部分CPLD器件具有ISP功能。例如,Akn公司的MAX7000S(5V)、 MAX7000A(3..3Ⅴ)和MAX7000B(2.5Ⅴ)系歹刂, Xilinx公司的XC9500系列以及Lathce公司的CPLD器件等。ISP器件的编程必须具各三个条件:ISP专用编程电缆、微机、ISP编程软件。编程时,用户首先将ISP编程电缆的一端接到微机的数据传输端口上①,另一端接到电路板上被编程器件的ISP接口上,然后通过编程软件发出编程命令,将编程数据传送到芯片中。

ISP接口也不完全相同,但基本上都支持中都设有JTAG规定的4个I/0引脚。各引脚.

TDO的数据可以用于编程校验,也可以作为多个CPLD串行编程时下一个CPLD器件的输入数据,如图7,3,7所示。多数CPLD的这4个编程引脚也可以作为用户I/0使用。

与后面将要介绍的FPGA相比,尽管CPLD在电路规模和灵活性方面不如FPGA,但是它的可加密性和传输延时预知性,使得CPLD仍广泛应用于数字系统设计中。

目前,各大生产厂商仍不断开发出集成度更高、速度更快(功耗更低的CPLD新产品,核心工作电源可以低到1.8V。表7.3.2所示为几种典型的CPLD产品。

可以是并口、串口或USB口,视编程软件所支持的端口而定。

系Joint Test Action Group的缩写,指由该组织制定的IEEE 1149,l接口标准。现场可编程门阵列(FPGA①)是⒛世纪80年代中期发展起来的另一种类型的可编程器件。它不像CPLD那样采用可编程的“与一或”阵列来实现逻辑函数,

系Field Programmable Gate Array的缩写。

公网安备44030402000607

公网安备44030402000607