GNT30-24G 输入/输出模块lOB

发布时间:2019/10/21 17:42:41 访问次数:918

GNT30-24G输入/输出模块lOB

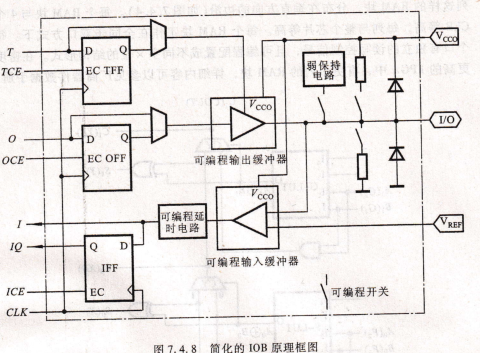

IOB是FPGA外部封装引脚和内部逻辑间的接口。每个IOB对应一个封装引脚,通过对IOB编程,可将引脚分别定义为输入、输出和双向功能。IOB的简化原理图如图7.4.8所示。图中的Ⅴcc。和ⅤREF引脚与其他IOB共用。IOB中有输人和输出两条信号通路。当I/0引脚用作输出时,内部逻辑信号由@端进人IOB模块,由可编程数据选择器确定是直接送输出缓冲器还是经过D触发器寄存后再送输出缓冲器。输出缓冲器使能控制信号r可以直接控制输出缓冲器,也可以通过触发器TFF后再控制输出缓冲器。当I/0引脚用作输入时,引脚上的输人信号经过输入缓冲器,可以直接由J进人内部逻辑电路,也可以经触发器IFF寄存后由四输人到内部逻辑电路中。没有用到的引脚被预置为高阻态。

可编程延时电路可以控制输入信号进人的时机,保证内部逻辑电路协调工作。其最短延迟时间为零。

3个触发器均可编程配置为边沿触发或电平触发方式,它们共用一个时钟信号CLK,但有各自的时钟使能控制信号。通过它们可以实现同步输入/输出。

输入、输出缓冲器和IOB中所有的信号,均有独立的极性控制电路(图7.4.8中未画出),可以控制信号是否反相,使能信号是高有效还是低有效,触发器是上升沿触发还是下降沿触发等。

图7.4,8中两个钳位二极管具有瞬时过压保护和静电保护作用。上拉电阻、下拉电阻和弱保持电路(Weakˉkeeper Circuit)可通过编程配置给I/o引脚。弱保持电路监视并跟踪1/0引脚输入电压的变化,当连至引脚总线上所有的驱动信号全部无效时,弱保持电路将维持在引脚最后一个状态的逻辑电平上,可以避免总线处于悬浮状态,消除总线抖动。

为使FPGA能在不同电源系统中正常工作,IOB中设计了两个电压输入端Vcc。和ⅤRm(它们由多个IOB共用)。VRⅢ为逻辑电平的参考电压,在执行某些I/0标准时,需要输人ⅤREF①。大约每6个I/o有一个VREF引脚。

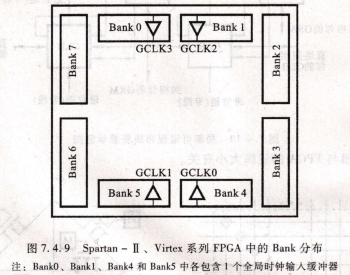

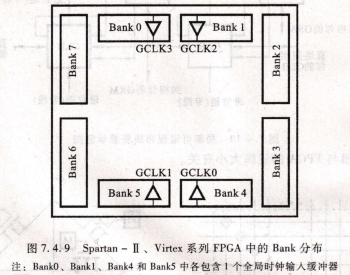

在此基础上,为了增强FPGA的适应性和灵活性,将若干个IOB组织在一起,构成一个组(Bank),如图7.4,9所示。一般FPGA的I/o划分为8个Bank。同一个Bank中Ⅴcc。引脚只能用同一个电压值,VRm也只能用同一个电压值。但不是所有VREF引脚都必须输人一个参考电压,即需要输入的接同一电压值,不需要输入的可以不接参考电压。FPGA的规模不同,每个Bank中Vcc。引脚和VRm引脚的数量也不相同。不同的Bank可以与不同I/0信号传输标准的逻辑电路进行接口。这一特性可以使FPGA工作在由不同工作电源构成的复杂系统中,而FPGA内部逻辑电路则在其所谓的核心电源(Core Powersupply①)下工作。

GNT30-24G输入/输出模块lOB

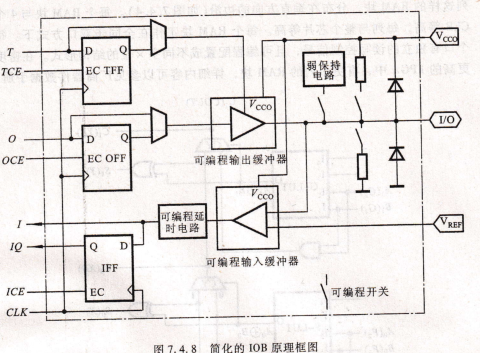

IOB是FPGA外部封装引脚和内部逻辑间的接口。每个IOB对应一个封装引脚,通过对IOB编程,可将引脚分别定义为输入、输出和双向功能。IOB的简化原理图如图7.4.8所示。图中的Ⅴcc。和ⅤREF引脚与其他IOB共用。IOB中有输人和输出两条信号通路。当I/0引脚用作输出时,内部逻辑信号由@端进人IOB模块,由可编程数据选择器确定是直接送输出缓冲器还是经过D触发器寄存后再送输出缓冲器。输出缓冲器使能控制信号r可以直接控制输出缓冲器,也可以通过触发器TFF后再控制输出缓冲器。当I/0引脚用作输入时,引脚上的输人信号经过输入缓冲器,可以直接由J进人内部逻辑电路,也可以经触发器IFF寄存后由四输人到内部逻辑电路中。没有用到的引脚被预置为高阻态。

可编程延时电路可以控制输入信号进人的时机,保证内部逻辑电路协调工作。其最短延迟时间为零。

3个触发器均可编程配置为边沿触发或电平触发方式,它们共用一个时钟信号CLK,但有各自的时钟使能控制信号。通过它们可以实现同步输入/输出。

输入、输出缓冲器和IOB中所有的信号,均有独立的极性控制电路(图7.4.8中未画出),可以控制信号是否反相,使能信号是高有效还是低有效,触发器是上升沿触发还是下降沿触发等。

图7.4,8中两个钳位二极管具有瞬时过压保护和静电保护作用。上拉电阻、下拉电阻和弱保持电路(Weakˉkeeper Circuit)可通过编程配置给I/o引脚。弱保持电路监视并跟踪1/0引脚输入电压的变化,当连至引脚总线上所有的驱动信号全部无效时,弱保持电路将维持在引脚最后一个状态的逻辑电平上,可以避免总线处于悬浮状态,消除总线抖动。

为使FPGA能在不同电源系统中正常工作,IOB中设计了两个电压输入端Vcc。和ⅤRm(它们由多个IOB共用)。VRⅢ为逻辑电平的参考电压,在执行某些I/0标准时,需要输人ⅤREF①。大约每6个I/o有一个VREF引脚。

在此基础上,为了增强FPGA的适应性和灵活性,将若干个IOB组织在一起,构成一个组(Bank),如图7.4,9所示。一般FPGA的I/o划分为8个Bank。同一个Bank中Ⅴcc。引脚只能用同一个电压值,VRm也只能用同一个电压值。但不是所有VREF引脚都必须输人一个参考电压,即需要输入的接同一电压值,不需要输入的可以不接参考电压。FPGA的规模不同,每个Bank中Vcc。引脚和VRm引脚的数量也不相同。不同的Bank可以与不同I/0信号传输标准的逻辑电路进行接口。这一特性可以使FPGA工作在由不同工作电源构成的复杂系统中,而FPGA内部逻辑电路则在其所谓的核心电源(Core Powersupply①)下工作。

公网安备44030402000607

公网安备44030402000607