MMBT2484 触发器的激励函数

发布时间:2019/10/21 17:46:31 访问次数:1938

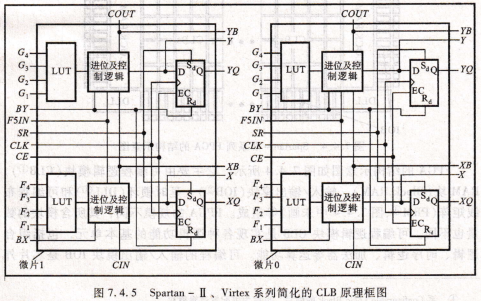

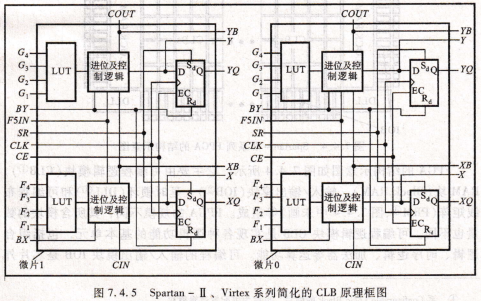

MMBT2484来自CLB以外布线区的4个输入变量同时送人F1~F4和相应的C1~C4,第5个输入变量送至BX端。F-LUT、G-LUT的输出和BX经数据选择器F5扩展为5变量逻辑函数。该结果可直接由F5端输出,也可经XMUX、DXMUX和D触发器,由X和/或X0端输出。

实现6变量任意逻辑函数,实现6变量任意逻辑函数需用2个微片。在实现5变量函数基础上,将另一个微片的乃的输出送入此微片的F5JⅣ输人端,第6个变量送人By端。数据选择器F5的输出、F5JⅣ和By经数据选择器F6扩展为6变量逻辑函数。该结果经YMUX、DYMUX和D触发器,由y和/或yQ端输出。

2位二进制加法器,由于加法运算涉及进位问题,所以CLB中专门设计了进位链,一个微片可以完成2位二进制数的加法运算。实现加法运算时,加数A1A。和被加数B1BO分别送入G2F2和G1F】,即C2=A1,Cl=B1,F2=A。,F1=BO。通过编

程使两个LUT分别实现F2①F1和C2①C1,同时编程使XMUx和YMUX选通异或门的输出,使xCMUX和YCMUX选通与门的输出,使YBMUX选通上端CY的输出。这样,图7.4,6可以简化为图7.4.7的形式。其中,低位的和S。=A0①BO①Ci,进位C0为

C0=(A0①B0)AOBO+(A0①BO)C~1

=(AOB0+AOBO)AOBO+(A0①B0)C~1

=A0BO+(A0+B0)C~1

高位的和及进位有相同的结果,由此看出,电路上、下两部分分别为两个全加器。

图7.4.6所示电路中的与门、ⅩCMUX、YCMUX、C~1^MUX和CY构成进位逻辑电路,也称进位链,可以与其他微片串联实现更多位的加法运算。当此微片为最低位时,通过编程使C~1MUX选通BX,且使Bx二0。

时序逻辑的实现,图7.4,6中触发器的输出,经布线区反馈给输人,再经LUT产生激励函数驱动触发器的D端,从而构成时序逻辑电路。触发器的激励函数也可通过

DXMUX(DYMUX)直接取自BX(By)。由多个CLB便可构成复杂的时序逻辑电路。

由于LUT就是一个16×1位的SRAM,所以CLB也可用来作存储器使用,不过此时LUT中的内容不再是预先配置好的,而是在正常工作时可以随时读写的,而且LUT不能再作为逻辑函数产生器使用。LUT也可以被设置成16位移位寄存器使用。另外,为弥补LUT构成RAM在容量上的不足,在FPGA中还增加了RAM块。这些RAM块以列的形式排列,在Spartan-Ⅱ系列中有两列这样的RAM块,分布在垂直方向的边沿(如图7.4.4)。每个RAM块与4个CLB等高,每列与整个芯片等高。每个RAM块工作在全同步双口方式下。每个口有独立的读写控制信号,且可编程配置成不同字×位的结构形式。在密度更高的FPGA中,有更多列的RAM块,详细内容可以参见厂商器件数据手册。

MMBT2484来自CLB以外布线区的4个输入变量同时送人F1~F4和相应的C1~C4,第5个输入变量送至BX端。F-LUT、G-LUT的输出和BX经数据选择器F5扩展为5变量逻辑函数。该结果可直接由F5端输出,也可经XMUX、DXMUX和D触发器,由X和/或X0端输出。

实现6变量任意逻辑函数,实现6变量任意逻辑函数需用2个微片。在实现5变量函数基础上,将另一个微片的乃的输出送入此微片的F5JⅣ输人端,第6个变量送人By端。数据选择器F5的输出、F5JⅣ和By经数据选择器F6扩展为6变量逻辑函数。该结果经YMUX、DYMUX和D触发器,由y和/或yQ端输出。

2位二进制加法器,由于加法运算涉及进位问题,所以CLB中专门设计了进位链,一个微片可以完成2位二进制数的加法运算。实现加法运算时,加数A1A。和被加数B1BO分别送入G2F2和G1F】,即C2=A1,Cl=B1,F2=A。,F1=BO。通过编

程使两个LUT分别实现F2①F1和C2①C1,同时编程使XMUx和YMUX选通异或门的输出,使xCMUX和YCMUX选通与门的输出,使YBMUX选通上端CY的输出。这样,图7.4,6可以简化为图7.4.7的形式。其中,低位的和S。=A0①BO①Ci,进位C0为

C0=(A0①B0)AOBO+(A0①BO)C~1

=(AOB0+AOBO)AOBO+(A0①B0)C~1

=A0BO+(A0+B0)C~1

高位的和及进位有相同的结果,由此看出,电路上、下两部分分别为两个全加器。

图7.4.6所示电路中的与门、ⅩCMUX、YCMUX、C~1^MUX和CY构成进位逻辑电路,也称进位链,可以与其他微片串联实现更多位的加法运算。当此微片为最低位时,通过编程使C~1MUX选通BX,且使Bx二0。

时序逻辑的实现,图7.4,6中触发器的输出,经布线区反馈给输人,再经LUT产生激励函数驱动触发器的D端,从而构成时序逻辑电路。触发器的激励函数也可通过

DXMUX(DYMUX)直接取自BX(By)。由多个CLB便可构成复杂的时序逻辑电路。

由于LUT就是一个16×1位的SRAM,所以CLB也可用来作存储器使用,不过此时LUT中的内容不再是预先配置好的,而是在正常工作时可以随时读写的,而且LUT不能再作为逻辑函数产生器使用。LUT也可以被设置成16位移位寄存器使用。另外,为弥补LUT构成RAM在容量上的不足,在FPGA中还增加了RAM块。这些RAM块以列的形式排列,在Spartan-Ⅱ系列中有两列这样的RAM块,分布在垂直方向的边沿(如图7.4.4)。每个RAM块与4个CLB等高,每列与整个芯片等高。每个RAM块工作在全同步双口方式下。每个口有独立的读写控制信号,且可编程配置成不同字×位的结构形式。在密度更高的FPGA中,有更多列的RAM块,详细内容可以参见厂商器件数据手册。

公网安备44030402000607

公网安备44030402000607