����ֵ��С�Ե�Դȥ��Ч����Ӱ��

����ʱ��:2017/6/22 19:54:26 ���ʴ���:441

����ֵ��С�Ե�Դȥ��Ч����Ӱ��

������������

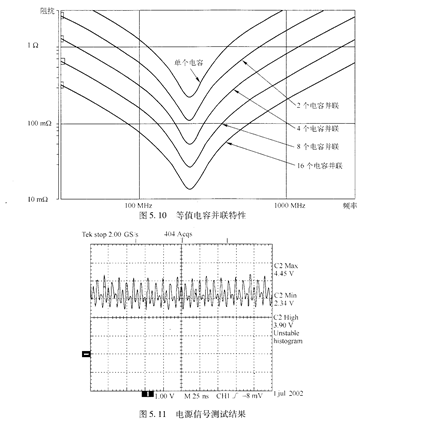

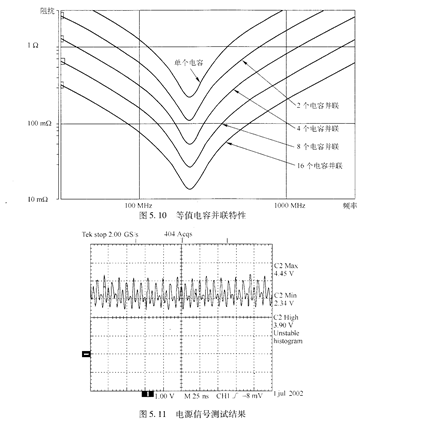

ʱ������оƬ����38",�ܶ����ֵ�·Ӳ����������ʦ������Ϥ,�����������(����������3.3������),M25P28V6G��ijһ�豸�ĵ�·�Ϲ���ʱ,�������Դ��������ʾ�������Ե���������ͼ5.11��ʾ��

��ͼ5.11�п��Կ���,���εķ�һ��ֵΪ1,8��,Ƶ�ʽӽ�100MHz,��Ȼ�����ϵ�Դ������Ҫ��(ͨ��Ҫ��Ϊ5%)����Դ�����ٽ�Ӱ���ŵ�Դƽ��͵�ƽ���������,������ϵͳ�Ĺ�ģ����Ҳ�кܴ��Ӱ�졣PCB���źŵĹ�ģ����ģ����ͼ5.12��ʾ���Ӹ�Ƶ�Ƕȿ���,�ο�ƽ��(������ƽ��͵�Դƽ�ڻ�������,�������κ�Ƶ�ʴ�С�ĵ�ѹ������ڲ�ģ����JDM��ӡ��������IJο�ƽ���ϻ��

ģ��ѹ��%M,��ͼ5.����ʾ�������ѹ��������,������ģ������M������,ͨ�����迹������ĵ������β��ϵĹ�ģ������

����ֵ��С�Ե�Դȥ��Ч����Ӱ��

������������

ʱ������оƬ����38",�ܶ����ֵ�·Ӳ����������ʦ������Ϥ,�����������(����������3.3������),M25P28V6G��ijһ�豸�ĵ�·�Ϲ���ʱ,�������Դ��������ʾ�������Ե���������ͼ5.11��ʾ��

��ͼ5.11�п��Կ���,���εķ�һ��ֵΪ1,8��,Ƶ�ʽӽ�100MHz,��Ȼ�����ϵ�Դ������Ҫ��(ͨ��Ҫ��Ϊ5%)����Դ�����ٽ�Ӱ���ŵ�Դƽ��͵�ƽ���������,������ϵͳ�Ĺ�ģ����Ҳ�кܴ��Ӱ�졣PCB���źŵĹ�ģ����ģ����ͼ5.12��ʾ���Ӹ�Ƶ�Ƕȿ���,�ο�ƽ��(������ƽ��͵�Դƽ�ڻ�������,�������κ�Ƶ�ʴ�С�ĵ�ѹ������ڲ�ģ����JDM��ӡ��������IJο�ƽ���ϻ��

ģ��ѹ��%M,��ͼ5.����ʾ�������ѹ��������,������ģ������M������,ͨ�����迹������ĵ������β��ϵĹ�ģ������

��һƪ����������

��һƪ��ʱ�Ӽ��������ֵ�ԭ��

�������

�������

- ���������ʪ����ʴ

- �ٵĿ�ʴ

- ������ĸɷ���ʴ

- ��TEOsΪ��Դ����sio2

- �����Ʊ�

- оƬ��������

- ��ƽ�е���֮��ľ������������ݵ�Ӱ��

- Ŀǰ�г��ϳ��ֵ�BGA��װ,�����������

- WLR�D�D��Ƭ���ɿ��Բ���

- ��������̽�

�Ƽ���������

�Ƽ���������

- ҵ��������PCM2702

- PGM2702����SSOP28��װ������С���ܣ�EP3... [��ϸ]

��������44030402000607

��������44030402000607