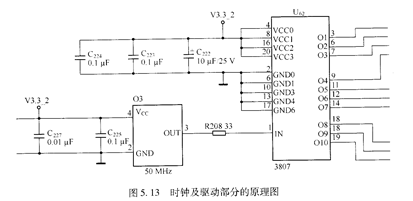

时钟及驱动部分的原理

发布时间:2017/6/22 19:56:24 访问次数:546

【原因分析】

时钟及驱动部分的原理图如图5.13所示。

图513 时钟及驱动部分的原理图M25P32V6P

经过分析电路原理图,发现给电源网络Ⅴ3.3~2去耦的电容(均为表贴)共有三个,一个10uF,在图514的A处;两个0.1uF,在图5.14的B和C处。经过初步检查后,问题定位为:PCB电源线布线较长,电容布局不合理,去耦电容没有靠近电源引脚,导致引线电感较大;电容值的选择不合理,0.1uF的电容的自谐振点远低于100MHz。

【原因分析】

时钟及驱动部分的原理图如图5.13所示。

图513 时钟及驱动部分的原理图M25P32V6P

经过分析电路原理图,发现给电源网络Ⅴ3.3~2去耦的电容(均为表贴)共有三个,一个10uF,在图514的A处;两个0.1uF,在图5.14的B和C处。经过初步检查后,问题定位为:PCB电源线布线较长,电容布局不合理,去耦电容没有靠近电源引脚,导致引线电感较大;电容值的选择不合理,0.1uF的电容的自谐振点远低于100MHz。

上一篇:电容值大小对电源去耦效果的影响

上一篇:典型的门电路输出级

公网安备44030402000607

公网安备44030402000607