��������

����ʱ��:2016/7/7 22:17:34 ���ʴ���:1673

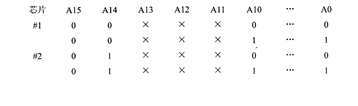

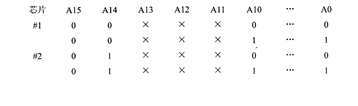

ȫ�����ǽ������ȫ����λ��ַ�߾��������������Ժ���Ϊ��оƬ��Ƭѡ�ź�,��ֻ��A2S60-A1-RH��λ��ַ�ߵ�һ���־��������������Ժ���Ϊ��оƬ��Ƭѡ�ź�,������Ƭѡ��ʽ��Ϊ�������롣����,Ҫ��4Ƭ2K��8λоƬ����8����8λ�洢��,����4ƬоƬ��Ҫ4��Ƭѡ�ź�,���Բ��â�4������,�������ӷ���ʾ��ͼ2.18��A13��A12��A11����λ,���Ը÷�����ÿ����Ԫ����8��ַ��û���õ��ĸ�λ��ַ(������A13A12A11)����Ϊ��0��,����ȷ���ĵ�ַ��ΪоƬ�ġ�������ַ����Ƭ1��Ƭ2�ĵ�ַ��������:

������,��������ʱ��оƬ��ַ����Ψһ��,Ҳ����˵�����ַ������ѡ��ͬһоƬ��ͬһ��Ԫ,�������ν�ĵ�ַ�ص��������ĵ�ַ�ص�,�����Щ��ַ�ڸ�ϵͳ�в�����������,���Ӱ����ϵͳ��ַ������Чʹ��,Ҳ�������˴洢������չ������ͼ2,18,����8K��8λ�洢��,��ռ����8��8K��8λ�洢�ռ�,������ѡ�ò�����ʱ,Ҫ�����ܶ�һЩ��λ��ַ�������롣

ȫ�����ǽ������ȫ����λ��ַ�߾��������������Ժ���Ϊ��оƬ��Ƭѡ�ź�,��ֻ��A2S60-A1-RH��λ��ַ�ߵ�һ���־��������������Ժ���Ϊ��оƬ��Ƭѡ�ź�,������Ƭѡ��ʽ��Ϊ�������롣����,Ҫ��4Ƭ2K��8λоƬ����8����8λ�洢��,����4ƬоƬ��Ҫ4��Ƭѡ�ź�,���Բ��â�4������,�������ӷ���ʾ��ͼ2.18��A13��A12��A11����λ,���Ը÷�����ÿ����Ԫ����8��ַ��û���õ��ĸ�λ��ַ(������A13A12A11)����Ϊ��0��,����ȷ���ĵ�ַ��ΪоƬ�ġ�������ַ����Ƭ1��Ƭ2�ĵ�ַ��������:

������,��������ʱ��оƬ��ַ����Ψһ��,Ҳ����˵�����ַ������ѡ��ͬһоƬ��ͬһ��Ԫ,�������ν�ĵ�ַ�ص��������ĵ�ַ�ص�,�����Щ��ַ�ڸ�ϵͳ�в�����������,���Ӱ����ϵͳ��ַ������Чʹ��,Ҳ�������˴洢������չ������ͼ2,18,����8K��8λ�洢��,��ռ����8��8K��8λ�洢�ռ�,������ѡ�ò�����ʱ,Ҫ�����ܶ�һЩ��λ��ַ�������롣

��һƪ��ȫ����

��һƪ���洢��Ԫ��λ��ͬʱ��չ

�������

�������

- ��������ע��ЧӦ�IJ�������

- �㶨�糡�ȱ�����С����

- �����������ֲ���ͳ�Ʒ���

- CMOs��·������ЧӦ(Lgch�Dup)

- ��������

- ͨ�������赲��Ľ����Ǿ��и��۵�����۽���

- ©ѩ����������

- CMOs���ɵ�·�Ļ������칤��

- �������IJ���

- ѹ�ӹ�װ

�Ƽ���������

�Ƽ���������

- Ƶ���ǵĽ������

- �ִ�Ƶ�����ڸ���Դģʽ��Ҳ����ʹ��Maker�͡�Mak... [��ϸ]

- ���١�����Դ���쵽���ͨ���Ŵ�

- 24λ��16λģ��ת������ADC0��

- ���ʡ���������˫��������Ƶ����Ŵ���Ӧ��

- �������������DRV8824

- ���ܿɱ��24.

- ���ɻ���ź�Ƭ��ϵͳMCUC8

- ��ý��Э������SM501��Ƕ��ʽϵͳ�е�Ӧ��

- ����IEEE802.11b��EPA�¶ȱ�����

- QUICCEngine�������ƶ�IP�������

- SoC���������IJ�ҵ����

- MPC8xxϵ�д�������Ƕ��ʽϵͳ��Դ���

- dsPIC�����ڽ�����Ƶ�����е�Ӧ���о�

��������44030402000607

��������44030402000607