FPGA逻辑功能设计

发布时间:2014/7/22 20:28:26 访问次数:567

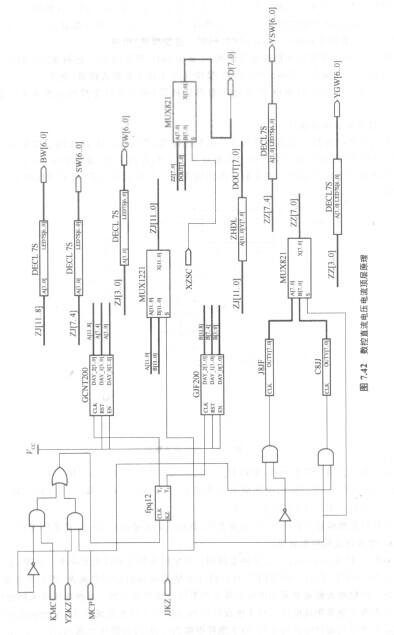

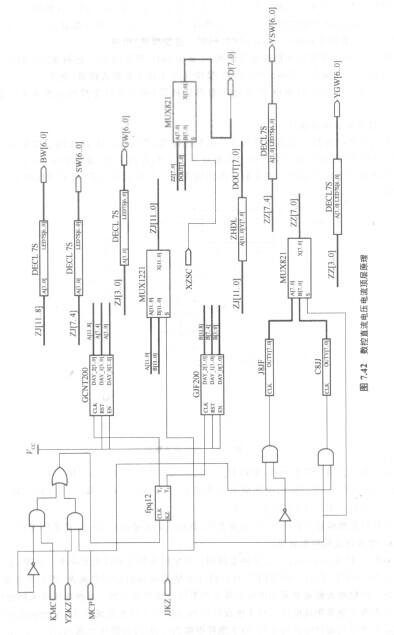

顶层原理图如图7. 42所示。

图7. 42中,输入:KMC为1024 Hz的脉冲,电流快速置数用;MCP为电压电流步进增加或减少脉冲;YZKZ为预置控制电平信号;JJKZ为电压电流步进增加或减少电平控制信号;XZSC为受控电压电流选择信号。 HD6475348F6输出:BW[60]SW[6―0]GW[6―0]为显示输出电流;D[7..0]为受控的电压电流数字量输出;YSW[6. OlYGW[6.O]为控制电流变化的数字量输出。

图7. 42中上半部分为数控电流输出,主要由yltfpq12模块(1到2分频器)、GCNT200(20-200进制加法计数器模块)、GJF200模块(200-20进制减法计数器)、MUX12 21模块(12个2选1数据选择器)、ZHDL( BCD码转二进制模块)组成。

图7. 42中下半部分为数控电压输出,主要由J8JF模块(8位二进制加法计数器)、C8JJ模块(8位二进制减法计数器)、MUX821模块(8个2选l数据选择器)组成。

右边的MUX821模块(8个2选1数据选择器)用于选择受控的

电流或电压数字量输出。

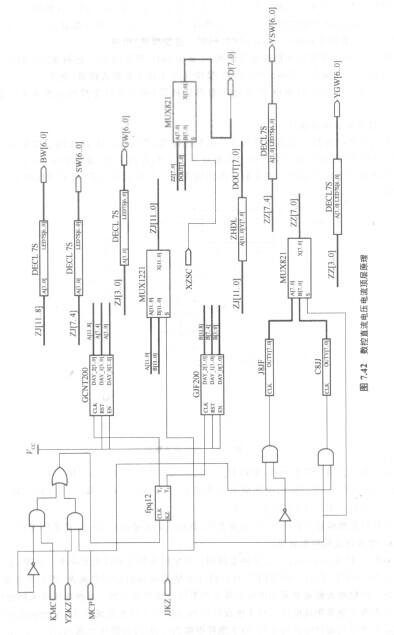

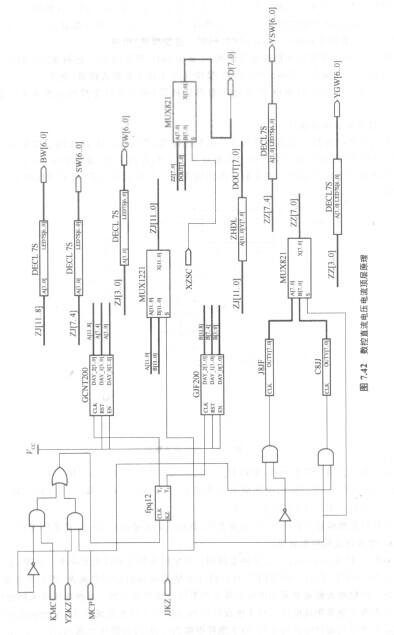

顶层原理图如图7. 42所示。

图7. 42中,输入:KMC为1024 Hz的脉冲,电流快速置数用;MCP为电压电流步进增加或减少脉冲;YZKZ为预置控制电平信号;JJKZ为电压电流步进增加或减少电平控制信号;XZSC为受控电压电流选择信号。 HD6475348F6输出:BW[60]SW[6―0]GW[6―0]为显示输出电流;D[7..0]为受控的电压电流数字量输出;YSW[6. OlYGW[6.O]为控制电流变化的数字量输出。

图7. 42中上半部分为数控电流输出,主要由yltfpq12模块(1到2分频器)、GCNT200(20-200进制加法计数器模块)、GJF200模块(200-20进制减法计数器)、MUX12 21模块(12个2选1数据选择器)、ZHDL( BCD码转二进制模块)组成。

图7. 42中下半部分为数控电压输出,主要由J8JF模块(8位二进制加法计数器)、C8JJ模块(8位二进制减法计数器)、MUX821模块(8个2选l数据选择器)组成。

右边的MUX821模块(8个2选1数据选择器)用于选择受控的

电流或电压数字量输出。

上一篇:数控直流稳压稳流电源

上一篇:稳压调节电路设计

热门点击

热门点击

- 二-十进制译码器

- LabVIEW的视觉VI及数字图像处理

- 公法线长度测量

- 零阶采样保持器

- 微分型单稳态触发器实验电路

- 自动打开DataSocket Server

- 关联维数计算

- 采样信号中噪声的影响与抑制

- 模糊规则库编辑器Rulebase-Edito

- 动态加载VI

推荐技术资料

推荐技术资料

- 自制智能型ICL7135

- 表头使ff11CL7135作为ADC,ICL7135是... [详细]

公网安备44030402000607

公网安备44030402000607