74LS293计数器

发布时间:2014/7/13 13:04:25 访问次数:5565

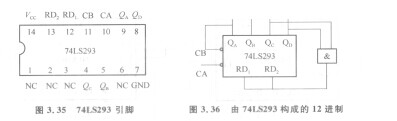

74LS293是2-8 -16进制计数器,SG3524DR是最大进制为16进制的异步计数器,其引脚如图3.35所示,CA、CB分别是内部第1、2级J-K触发器的触发输入端,RD.、RD2是直接置零端。当RD.、RD。=1时,内部4个J-K触发器全部置零。内部第1级触发器(CA输入、QA输出)是独立的,相当于二进制,后3级已经连成异步八进制计数器。如果QA和CB相连,就构成16进制加法计数器。

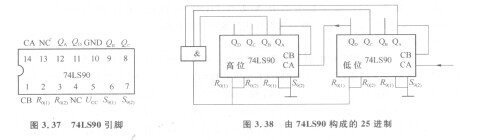

可以用74LS293设计任意进制计数器,比如设计12进制,在计数到12(即QDQcQBQA―1100)时,立刻置零,如图3.36所示。

74LS90计数器

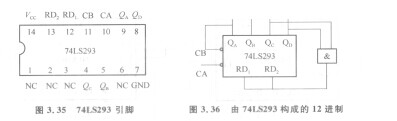

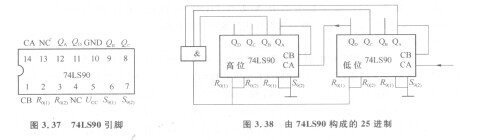

74LS90是十进制异步计数器,其内部由二进制和五进制计数器两部分组成,CA、CB分别是前部分二进制计数器和后部分五进制计数器的时钟输入端,R。c-,和R。c z,是直接置0端。,器件被置O,即QDQcQ。QA一0000。S是置9端。当50(1).S0(2) =1时,器件被置9,即QDQcQBQA一1001。Rocl)、R0(2)、So(1)、So(2)全为0时正常计数,当QA和CB相连,CA输入时钟时,为十进制计数器,74LS90器件引脚和由此构成的25进制计数器如图3. 37和图3.38所示。

74LS293是2-8 -16进制计数器,SG3524DR是最大进制为16进制的异步计数器,其引脚如图3.35所示,CA、CB分别是内部第1、2级J-K触发器的触发输入端,RD.、RD2是直接置零端。当RD.、RD。=1时,内部4个J-K触发器全部置零。内部第1级触发器(CA输入、QA输出)是独立的,相当于二进制,后3级已经连成异步八进制计数器。如果QA和CB相连,就构成16进制加法计数器。

可以用74LS293设计任意进制计数器,比如设计12进制,在计数到12(即QDQcQBQA―1100)时,立刻置零,如图3.36所示。

74LS90计数器

74LS90是十进制异步计数器,其内部由二进制和五进制计数器两部分组成,CA、CB分别是前部分二进制计数器和后部分五进制计数器的时钟输入端,R。c-,和R。c z,是直接置0端。,器件被置O,即QDQcQ。QA一0000。S是置9端。当50(1).S0(2) =1时,器件被置9,即QDQcQBQA一1001。Rocl)、R0(2)、So(1)、So(2)全为0时正常计数,当QA和CB相连,CA输入时钟时,为十进制计数器,74LS90器件引脚和由此构成的25进制计数器如图3. 37和图3.38所示。

上一篇:74LS90计数器

公网安备44030402000607

公网安备44030402000607