嵌入式电容的实际应用

发布时间:2014/4/17 21:26:28 访问次数:784

1989-1990年Zycon(Zycon自那以后成为Hadco,现在是Sanmina)利用标准的FR-4环氧玻璃作为电介质,开发了具有2mils层间距的特殊的PCB层压板。 HD74LS04P这个被称为ZBC-2000的层压板提供500pF/in2的层间电容“。在一个PCB中用两组由这种层压板制成的电源和地平面,可以获得所希望的lOOOpF/inz的电容。

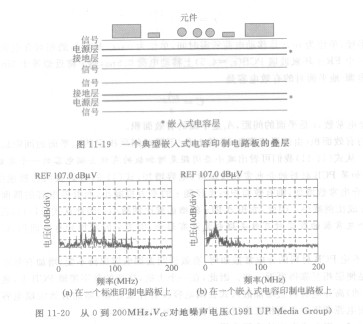

虽然Sanmina( Howard和Lucas,1992)和Unisys( Sisler,19 91)对2mils厚的嵌入式电容印制电路板申请了专利,这个技术很容易用而且是多源的。Sanmina的这个技术的商业命名是嵌入式电容。虽然这个技术应用已超过15年,它只是现在才流行起来。转换到嵌入式电容PCB是简单的,因为不需要新的工艺,只是叠层发生改变。因此制作两套原型板就很容易检验这种技术,一套板用标准方法制作,第二套板用嵌入式电容层制作,所以两套板的性能可以直接比较。最~般的叠层如图11-19所示。

如16.4.2节将讨论的,另一种叠层也可能用到嵌入式电容方法。因为两个I 平面对的应用,当应用嵌入式电容时,四层板变成六层板,六层板变成八层板。虽然罢蓬蒜。层压板比标准PCB层压板稍贵些,主要的成本增加来自必须印制两个额外的PCB层。

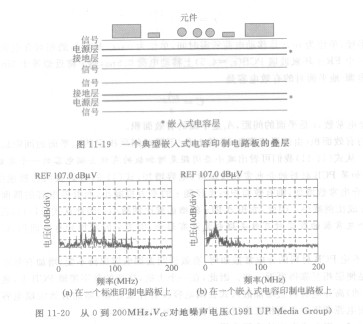

图11-20表示用图11-19所示叠层的一个嵌入式电容PCB上和另外一个只有一个电源平面和一个接地平面(Sisler,19 91)的相同的标准(非嵌入式电容)板上,从1~200MHzVc。对地噪声电压。比较图11-20中的两个图可看出嵌入式电容板在高于30MHz的所有频率噪声减小得更多,在高于60MHz时几乎没有可测噪声。对于图11-20所示的数据,标准板上有135个然而,当频率低30MHz,尤其在20MHz,嵌入式电容板上去耦较差。这是由于在这些低频率嵌入式电容板没有足够的总电容以使其有效所导致的结果。这个结果与图11-12的所示结果相似,即增加电容的数量减小了电源分布网络的高频阻抗,但没有减小低频阻抗。为了减小低频阻抗,通过比较图11-12和图11-13证明需要额外的电容。

对于图11-20(b)所示的情况,将原来的135个去耦电容恢复4个(因而增加了总电容)以把嵌入式电容板上的低频噪声电压减小到标准板上的水平。

后来其他人在嵌入式电容印制电路板上的测试已表明在频率高达5GHz时,在板上只有很少或没有离散去耦电容的情况下能提供有效的去耦。我不知道是谁已进行丁5GHz以上的测试,但没有理由怀疑嵌入式电容方法即使高于这个频率会失效。

嵌入式电容板也有其他的优点。因为层间距的减小,也因为多个电源和接地平面的应用,使电源和接地平面的电感显著减小。因为嵌入式电容电源/接地平面的三明治筝穆作为低L/C比率的结果(见式(10-3》而趋于一个低Q结构,所以谐振问题也减到最小。瓷外,通过去掉90%或更多的去耦电容以及与它们相关的导通孑L,板的布线大大简化,而且在许多情况下板的尺寸可以减小。在一些应用中,去掉大部分离散的去耦电容也会消除在板的两个面上对表面安装组件的需求。

嵌入式电容板通常在板上所有位置有相似的电源对地噪声电压,而使用离散去耦电容的标准板的电源对地噪声电压取决于测量的位置。

1989-1990年Zycon(Zycon自那以后成为Hadco,现在是Sanmina)利用标准的FR-4环氧玻璃作为电介质,开发了具有2mils层间距的特殊的PCB层压板。 HD74LS04P这个被称为ZBC-2000的层压板提供500pF/in2的层间电容“。在一个PCB中用两组由这种层压板制成的电源和地平面,可以获得所希望的lOOOpF/inz的电容。

虽然Sanmina( Howard和Lucas,1992)和Unisys( Sisler,19 91)对2mils厚的嵌入式电容印制电路板申请了专利,这个技术很容易用而且是多源的。Sanmina的这个技术的商业命名是嵌入式电容。虽然这个技术应用已超过15年,它只是现在才流行起来。转换到嵌入式电容PCB是简单的,因为不需要新的工艺,只是叠层发生改变。因此制作两套原型板就很容易检验这种技术,一套板用标准方法制作,第二套板用嵌入式电容层制作,所以两套板的性能可以直接比较。最~般的叠层如图11-19所示。

如16.4.2节将讨论的,另一种叠层也可能用到嵌入式电容方法。因为两个I 平面对的应用,当应用嵌入式电容时,四层板变成六层板,六层板变成八层板。虽然罢蓬蒜。层压板比标准PCB层压板稍贵些,主要的成本增加来自必须印制两个额外的PCB层。

图11-20表示用图11-19所示叠层的一个嵌入式电容PCB上和另外一个只有一个电源平面和一个接地平面(Sisler,19 91)的相同的标准(非嵌入式电容)板上,从1~200MHzVc。对地噪声电压。比较图11-20中的两个图可看出嵌入式电容板在高于30MHz的所有频率噪声减小得更多,在高于60MHz时几乎没有可测噪声。对于图11-20所示的数据,标准板上有135个然而,当频率低30MHz,尤其在20MHz,嵌入式电容板上去耦较差。这是由于在这些低频率嵌入式电容板没有足够的总电容以使其有效所导致的结果。这个结果与图11-12的所示结果相似,即增加电容的数量减小了电源分布网络的高频阻抗,但没有减小低频阻抗。为了减小低频阻抗,通过比较图11-12和图11-13证明需要额外的电容。

对于图11-20(b)所示的情况,将原来的135个去耦电容恢复4个(因而增加了总电容)以把嵌入式电容板上的低频噪声电压减小到标准板上的水平。

后来其他人在嵌入式电容印制电路板上的测试已表明在频率高达5GHz时,在板上只有很少或没有离散去耦电容的情况下能提供有效的去耦。我不知道是谁已进行丁5GHz以上的测试,但没有理由怀疑嵌入式电容方法即使高于这个频率会失效。

嵌入式电容板也有其他的优点。因为层间距的减小,也因为多个电源和接地平面的应用,使电源和接地平面的电感显著减小。因为嵌入式电容电源/接地平面的三明治筝穆作为低L/C比率的结果(见式(10-3》而趋于一个低Q结构,所以谐振问题也减到最小。瓷外,通过去掉90%或更多的去耦电容以及与它们相关的导通孑L,板的布线大大简化,而且在许多情况下板的尺寸可以减小。在一些应用中,去掉大部分离散的去耦电容也会消除在板的两个面上对表面安装组件的需求。

嵌入式电容板通常在板上所有位置有相似的电源对地噪声电压,而使用离散去耦电容的标准板的电源对地噪声电压取决于测量的位置。

公网安备44030402000607

公网安备44030402000607