电源隔离

发布时间:2014/4/17 21:29:14 访问次数:611

对于高频去耦问题唯一真正的解决方法是在PCB内使用多个离散或嵌入式电容。

虽然另一个方法不解决基本的去耦问题,HD74LS157RPEL-E-Q 但它可以且已被应用于使较差去耦的不利影响最小化。目的是防止由去耦失效导致的噪声电源平面干扰PCB的其他部分。

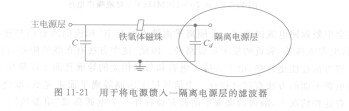

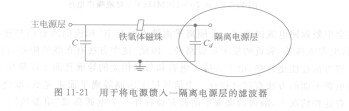

将PCB电源层的噪声部分与其他部分绝缘或分割,并通过一个兀型滤波器给隔离平面馈电可达到这一目的,如图11-21所示。注意到只是电源层被分割开,而不是接地层。这个方法在隔离的电源层上不能减小噪声或提高去耦有效性,但它防止这个噪声污染主要的电源层。

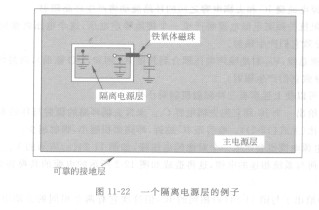

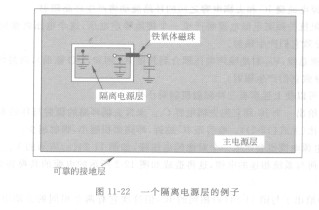

当只是一小部分电路工作于高频时,这个方法最有效。高频电路或一组电路与电路的其余部分隔离,且从隔离的电源平面馈电,如图11-22所示。例如,如果一个微处理器是唯一工作于高时钟频率的芯片,则这个微处理器和它的时钟振荡器可能从被隔离的电源平面上馈入能量。另一个例子是将时钟振荡器和时钟驱动与电路的其他部分隔离,且从一个被隔离的电源平面上馈入能量。多个被隔离的电源平面也可被用于不同的电路。

图11-23给出在一个由隔离平面供电的微处理器和它的振荡电路的PCB上,从20~120MHz Vcc对地噪声电压。图11-23 (a)给出在给微处理器供电的隔离平面上VCC对地噪声电压,图ll-23(b)给出了主电源层上的V。c对地噪声电压。在图11-23 (a)中,我们看到微处理器的无效去耦产生大量的时钟噪声。将图11-23 (a)和图11-23 (b)进行比较,我们看到与被隔离的电源平面上的噪声相比较,在60MHz以上在主Vcc平面上的时钟噪声实际上已排除,低于60MHz时噪声也减小很多。

对于高频去耦问题唯一真正的解决方法是在PCB内使用多个离散或嵌入式电容。

虽然另一个方法不解决基本的去耦问题,HD74LS157RPEL-E-Q 但它可以且已被应用于使较差去耦的不利影响最小化。目的是防止由去耦失效导致的噪声电源平面干扰PCB的其他部分。

将PCB电源层的噪声部分与其他部分绝缘或分割,并通过一个兀型滤波器给隔离平面馈电可达到这一目的,如图11-21所示。注意到只是电源层被分割开,而不是接地层。这个方法在隔离的电源层上不能减小噪声或提高去耦有效性,但它防止这个噪声污染主要的电源层。

当只是一小部分电路工作于高频时,这个方法最有效。高频电路或一组电路与电路的其余部分隔离,且从隔离的电源平面馈电,如图11-22所示。例如,如果一个微处理器是唯一工作于高时钟频率的芯片,则这个微处理器和它的时钟振荡器可能从被隔离的电源平面上馈入能量。另一个例子是将时钟振荡器和时钟驱动与电路的其他部分隔离,且从一个被隔离的电源平面上馈入能量。多个被隔离的电源平面也可被用于不同的电路。

图11-23给出在一个由隔离平面供电的微处理器和它的振荡电路的PCB上,从20~120MHz Vcc对地噪声电压。图11-23 (a)给出在给微处理器供电的隔离平面上VCC对地噪声电压,图ll-23(b)给出了主电源层上的V。c对地噪声电压。在图11-23 (a)中,我们看到微处理器的无效去耦产生大量的时钟噪声。将图11-23 (a)和图11-23 (b)进行比较,我们看到与被隔离的电源平面上的噪声相比较,在60MHz以上在主Vcc平面上的时钟噪声实际上已排除,低于60MHz时噪声也减小很多。

上一篇:嵌入式电容的实际应用

上一篇:在隔离电源平面上

公网安备44030402000607

公网安备44030402000607