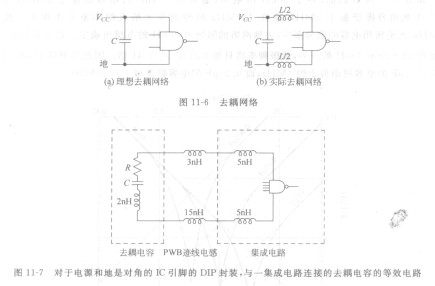

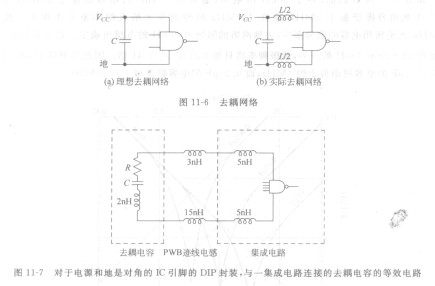

对于电源和地是对角的IC引脚的DIP封装

发布时间:2014/4/17 20:52:06 访问次数:1404

极其重要的是IC和去耦电容间迹线电感的最小化。印制电路迹线应该尽可能地短,HCF4052M013TR且应该设置得尽可能地靠近在一起以使环路面积最小化。从图11-7中也注意到去耦电容对电感的贡献最小。因此,这不是主要的问题。从上面我们也看到总电感可从低的约lOnH变化到高的40nH。通常,变化范围是15~30nH。正是这个电感限制了去耦网络的有效性。重要的是记住这个事实――我们在电源和地之间设置了一个L-C网络而不是一个电容!

因为电容和电感的组合,去耦网络在一些频率点将发生谐振。在谐振频率,感抗的大小等于容抗的大小,网络具有非常低的阻抗且是一个有效的旁路。高于谐振频率时,电路成为电感性的,阻抗随频率增大。

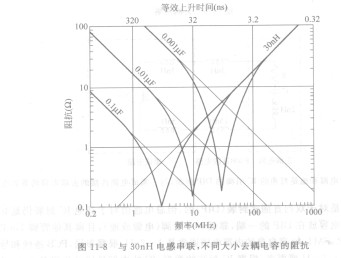

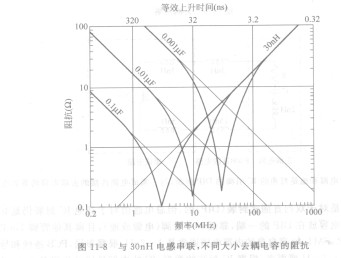

图11-8表示当串联30nH的电感时不同去耦电容的阻抗随频率的变化。顶部的水平刻度表明对应于底部的水平刻度所示频率的等效数字逻辑的上升时间。

容抗等于感抗的点是电感和电容组合的谐振频率点。在谐振点阻抗减小到一个小的值(恰等于网络的串联电阻),因为容抗抵消了感抗,所以只剩电阻。

如图11-8历看到的,对于30nH的电感,通常用0.lpLF的电容谐振于3MHz,而用 o.OlyF的电容将谐振于9MHz,这在100MHz时钟的今天给人的印象并不深刻。超过50MHz,无论所用电容的值为多少,去耦网络的阻抗由30nH的电感所确定。如果布局好,电感是图11-8所示30nH的一半,谐振频率将只增加厄倍,或1. 41倍。因此当串联15nH的电感时,0.1弘F的电容将谐振于约4MHz,而0.OltiF的电容将谐振于约13MHz。

极其重要的是IC和去耦电容间迹线电感的最小化。印制电路迹线应该尽可能地短,HCF4052M013TR且应该设置得尽可能地靠近在一起以使环路面积最小化。从图11-7中也注意到去耦电容对电感的贡献最小。因此,这不是主要的问题。从上面我们也看到总电感可从低的约lOnH变化到高的40nH。通常,变化范围是15~30nH。正是这个电感限制了去耦网络的有效性。重要的是记住这个事实――我们在电源和地之间设置了一个L-C网络而不是一个电容!

因为电容和电感的组合,去耦网络在一些频率点将发生谐振。在谐振频率,感抗的大小等于容抗的大小,网络具有非常低的阻抗且是一个有效的旁路。高于谐振频率时,电路成为电感性的,阻抗随频率增大。

图11-8表示当串联30nH的电感时不同去耦电容的阻抗随频率的变化。顶部的水平刻度表明对应于底部的水平刻度所示频率的等效数字逻辑的上升时间。

容抗等于感抗的点是电感和电容组合的谐振频率点。在谐振点阻抗减小到一个小的值(恰等于网络的串联电阻),因为容抗抵消了感抗,所以只剩电阻。

如图11-8历看到的,对于30nH的电感,通常用0.lpLF的电容谐振于3MHz,而用 o.OlyF的电容将谐振于9MHz,这在100MHz时钟的今天给人的印象并不深刻。超过50MHz,无论所用电容的值为多少,去耦网络的阻抗由30nH的电感所确定。如果布局好,电感是图11-8所示30nH的一半,谐振频率将只增加厄倍,或1. 41倍。因此当串联15nH的电感时,0.1弘F的电容将谐振于约4MHz,而0.OltiF的电容将谐振于约13MHz。

上一篇:去耦电容

上一篇:对于有和没有去耦电容的印制电路板

热门点击

热门点击

- 辫线(猪尾巴线)

- 电子管屏极特性曲线

- 放大器增益不足故障分析

- MD机原理

- 判断输出电压极性方法

- 吸锡电烙铁拆卸集成电路的方法

- 对于电源和地是对角的IC引脚的DIP封装

- 分立元器件BTL功率放大器原理电路

- 薄屏蔽层内的多重反射

- 电路板上元器件焊接方法

推荐技术资料

推荐技术资料

- 自制智能型ICL7135

- 表头使ff11CL7135作为ADC,ICL7135是... [详细]

公网安备44030402000607

公网安备44030402000607