对于有和没有去耦电容的印制电路板

发布时间:2014/4/17 20:54:27 访问次数:611

图11-8清晰地表明不管电容值或位置如何,靠近HCF4053M013TR放一个电容,在50MHz以上频率,不是数字逻辑去耦的一个有效方法,图11-8也表明对于低于大约50MHz的频率,在出问题的频率上通过选择不同的电容值以设置谐振下降点,从而可能对去耦网络进行调谐。但在50MHz以上同样的方法将不再有效。

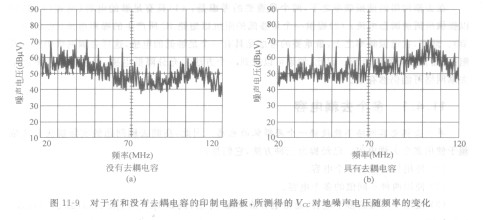

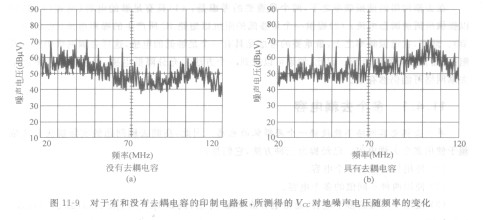

图11-9表明在板上用0.OluF的去耦电容,VCc对地噪声电压的测量值随频率的变化。测量是在板上有和没有去耦电容的两种情况下,在IC的电源和接地插脚间进行的。在频率范围为20~70MHz时,去耦电容的存在显著地降低了VCc对地噪声电压的大小。然而,在频率范围为70~120MHz时,有和没有去耦电容时,噪声电压是一样的,这个结果表明在这个频率范围内电容是无效的,预测的结果通过图11-8得到证实。

图11-8清晰地表明不管电容值或位置如何,靠近HCF4053M013TR放一个电容,在50MHz以上频率,不是数字逻辑去耦的一个有效方法,图11-8也表明对于低于大约50MHz的频率,在出问题的频率上通过选择不同的电容值以设置谐振下降点,从而可能对去耦网络进行调谐。但在50MHz以上同样的方法将不再有效。

图11-9表明在板上用0.OluF的去耦电容,VCc对地噪声电压的测量值随频率的变化。测量是在板上有和没有去耦电容的两种情况下,在IC的电源和接地插脚间进行的。在频率范围为20~70MHz时,去耦电容的存在显著地降低了VCc对地噪声电压的大小。然而,在频率范围为70~120MHz时,有和没有去耦电容时,噪声电压是一样的,这个结果表明在这个频率范围内电容是无效的,预测的结果通过图11-8得到证实。

上一篇:有效的去耦策略

公网安备44030402000607

公网安备44030402000607