去耦电容

发布时间:2014/4/17 20:48:51 访问次数:585

时钟频率的增大以及更快的上升时间都将导致有效的电源去耦变得更加困难。无效的去HCF4050M013TR耦可以导致过多的电源总线噪声以及过多的辐射发射。

许多设计者通过在靠近IC处放一个0.lFeF或0.OlruF的电容来对数字逻辑IC进行去耦。这个方法与被用于数字逻辑IC已50年的方法是相同的,所以它必然仍是正确的方法,对吗?然而,在这过去的50年内IC科技发生了多大的变化?我认为有趣的是这个方法已应用了这么多年。可能没有人惊讶我们现在提出一种数字IC去耦新的方法是必要的。 、

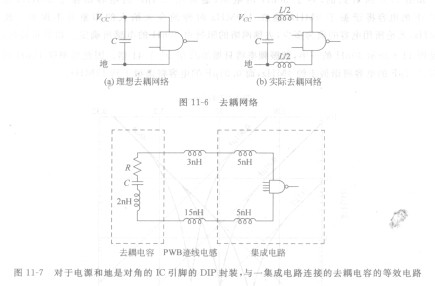

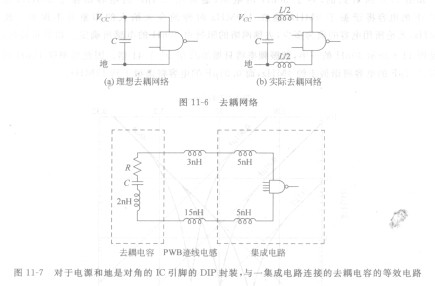

重要的是要理解去耦不是如图11-6 (a)所示的靠近IC放一个电容以提供瞬态开关电流这样的过程;而是靠近IC放一个L-C网络以提供瞬态开关电流的过程,如图ll-6(b)所示。所有的去耦电容都有与其串联的电感。因此,去耦网络是一个串联谐振电路。如图11-7所示,电感来自如下所示的三种源:

(1)电容本身;

(2) PCB迹线和导通孔的互相连接;

(3) IC内部的导线结构。

图11-7对于电源和地是对角的IC引脚的DIP封装,与一集成电路连接的去耦电容的等效电路虽然图11-7是对于双列直插式封装(DIP)的,但总电感值对于其他IC封装仍是有代表性的。图11-7假设电容放在DIP的一端,靠近一个管脚(电源或地),且离其他管脚lin以外。

表面贴装技术(SMT)电容自身的内部电感通常是1~2nH,根据布局,PCB迹线和导通孔的互相连接约增加5~20nH或更多,根据IC封装的类型,IC的内部导线结构可具有3~15nH的电感。然而,互相连接的PCB迹线的电感通常是在系统设计者的控制之下的唯一参数。

时钟频率的增大以及更快的上升时间都将导致有效的电源去耦变得更加困难。无效的去HCF4050M013TR耦可以导致过多的电源总线噪声以及过多的辐射发射。

许多设计者通过在靠近IC处放一个0.lFeF或0.OlruF的电容来对数字逻辑IC进行去耦。这个方法与被用于数字逻辑IC已50年的方法是相同的,所以它必然仍是正确的方法,对吗?然而,在这过去的50年内IC科技发生了多大的变化?我认为有趣的是这个方法已应用了这么多年。可能没有人惊讶我们现在提出一种数字IC去耦新的方法是必要的。 、

重要的是要理解去耦不是如图11-6 (a)所示的靠近IC放一个电容以提供瞬态开关电流这样的过程;而是靠近IC放一个L-C网络以提供瞬态开关电流的过程,如图ll-6(b)所示。所有的去耦电容都有与其串联的电感。因此,去耦网络是一个串联谐振电路。如图11-7所示,电感来自如下所示的三种源:

(1)电容本身;

(2) PCB迹线和导通孔的互相连接;

(3) IC内部的导线结构。

图11-7对于电源和地是对角的IC引脚的DIP封装,与一集成电路连接的去耦电容的等效电路虽然图11-7是对于双列直插式封装(DIP)的,但总电感值对于其他IC封装仍是有代表性的。图11-7假设电容放在DIP的一端,靠近一个管脚(电源或地),且离其他管脚lin以外。

表面贴装技术(SMT)电容自身的内部电感通常是1~2nH,根据布局,PCB迹线和导通孔的互相连接约增加5~20nH或更多,根据IC封装的类型,IC的内部导线结构可具有3~15nH的电感。然而,互相连接的PCB迹线的电感通常是在系统设计者的控制之下的唯一参数。

上一篇:动态内部电流

公网安备44030402000607

公网安备44030402000607