主从觖发器

发布时间:2012/12/8 19:01:57 访问次数:937

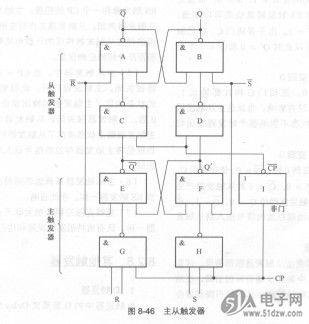

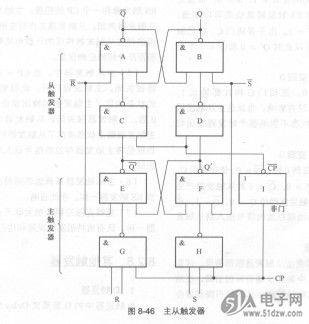

图8-46所示是主从RS触MMSP430F169IPMR发器电路。从电路中可看出共有8个与非门和1个非门构成这种触发器。其中与非门A、B、C和D构成同步RS触发器电路,又称为从触发器:与非门E、F、G和H构成另一个同步RS触发器,称为主触发器。二者合起来称为主从触发器。非门I对CP进行倒相处理。

在主从触发器中,Q和Q是它的两个输出端,也是从触发器的输出端;Q和Q 7是主触发器的输出端。这一触发器的工作原理可以分成下列几步来分析。

1.互补时钟脉冲信号

时钟脉冲CP加到与非门G、H输入端,用来触发主触发器,与此同时CP还加到了非门I输入端,其输出端输出的CP加到与非门C、D输入端,用来触发从触发器。CP和CP(为逻辑门I的输出信号)一对时钟脉冲称为互补时钟脉冲信号,其中CP触发主触发器,CP触发从触发器。

2.当CP =1时的电路分析

在CP=1时,逻辑门I输出0,将逻辑门C、D关闭,这样在CP=1的整个期间,逻辑门A、B、C和D构成的从触发器输出状态保持不变,即无论主触发器输出端Q’和Q’的状态怎样变化,整个主从触发器的输出端Q和Q都不变。

在CP=1期间设R=1,S=O,根据上面所介绍的同步RS触发器真值表可以知道,此时Q=0,Q=1。由于逻辑门C、D已被CP=0关闭,所以此时Q 7=0和Q’=1不能触发从触发器。

3.CP从1变到0

由于CP=0,逻辑门G和H都输出1,对逻辑门E和F没有影响,也就是主从触发器输入端R、S的状态不影响整个触发器输出湍Q和Q的输出。

4.CP从1变到0

在CP从1变到0后,Cp=0,使逻辑门C、D打开,这时Q=0,Q=1对从触发器产生有效触发,使从触发器输出Q=O,Q=1,也就是主触发器输出端存放的信号送入到从触发器中。

图8-46所示是主从RS触MMSP430F169IPMR发器电路。从电路中可看出共有8个与非门和1个非门构成这种触发器。其中与非门A、B、C和D构成同步RS触发器电路,又称为从触发器:与非门E、F、G和H构成另一个同步RS触发器,称为主触发器。二者合起来称为主从触发器。非门I对CP进行倒相处理。

在主从触发器中,Q和Q是它的两个输出端,也是从触发器的输出端;Q和Q 7是主触发器的输出端。这一触发器的工作原理可以分成下列几步来分析。

1.互补时钟脉冲信号

时钟脉冲CP加到与非门G、H输入端,用来触发主触发器,与此同时CP还加到了非门I输入端,其输出端输出的CP加到与非门C、D输入端,用来触发从触发器。CP和CP(为逻辑门I的输出信号)一对时钟脉冲称为互补时钟脉冲信号,其中CP触发主触发器,CP触发从触发器。

2.当CP =1时的电路分析

在CP=1时,逻辑门I输出0,将逻辑门C、D关闭,这样在CP=1的整个期间,逻辑门A、B、C和D构成的从触发器输出状态保持不变,即无论主触发器输出端Q’和Q’的状态怎样变化,整个主从触发器的输出端Q和Q都不变。

在CP=1期间设R=1,S=O,根据上面所介绍的同步RS触发器真值表可以知道,此时Q=0,Q=1。由于逻辑门C、D已被CP=0关闭,所以此时Q 7=0和Q’=1不能触发从触发器。

3.CP从1变到0

由于CP=0,逻辑门G和H都输出1,对逻辑门E和F没有影响,也就是主从触发器输入端R、S的状态不影响整个触发器输出湍Q和Q的输出。

4.CP从1变到0

在CP从1变到0后,Cp=0,使逻辑门C、D打开,这时Q=0,Q=1对从触发器产生有效触发,使从触发器输出Q=O,Q=1,也就是主触发器输出端存放的信号送入到从触发器中。

公网安备44030402000607

公网安备44030402000607