模拟管脚的ESD保护设计

发布时间:2012/4/22 16:57:34 访问次数:1247

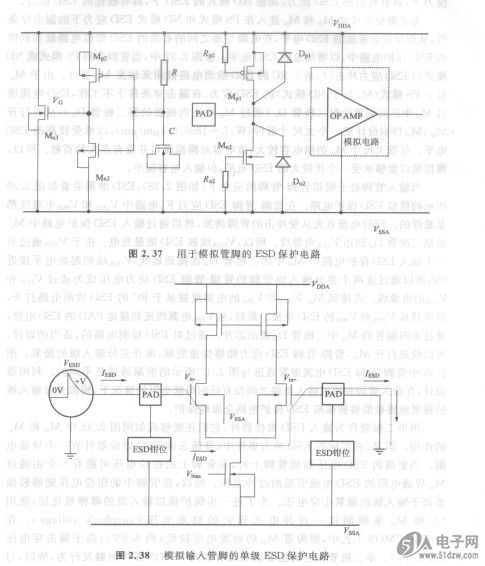

用于模拟PAD管脚的ESD保护UC3843电路如图2.37所示,采用0.35 ptm硅化物CMOS单元库的实际版图结构。器件漏区的寄生结电容。为了减少模拟管脚的输入电容,都设计得非常小,其宽长比仅为5010.5(肛m/_um)。在该0.35/um硅化物CMOS工艺中,宽长比为50/0.5(ym/“m)的栎准NMOS管,在PS-模式的ESD的应力下(NMOS管在漏击穿条件下),HBM ESD电平低于500V。但是这样一个小的NMOS管,在同样的0.35Um硅化物CMOS工艺中,能够承8000V的ESD电平,而NMOS管在NS-模式的ESD的应力下(NMOS管在漏二极管正向的条件下)。所以一个NMOS在PS模式和NS模式下,ESD电平相差很大。类似地,一个小尺寸的PMOS管在PD模式的应力下,具有较高的ESD能力,而在ND模式的ESD下,具有较低的ESD能力。

为了避免小尺寸Mn1和Mp1进入在PS模式和ND模式ESD应力下的漏击穿条件,从而导致非常低的ESD电平,在电源与地之间的有效的ESD钳位电路被加到模拟ESD保护电路中,以增加总的ESD电平。在图2.37中,当管脚受到PS模式或ND模式的ESD应力冲击时,基于RC的ESD检测电路被用来触发M。。器件。由于Mp1处于PS模式(Mn1处于ND模式)的ESD应力,在漏击穿条件下不工作,ESD电流通过Mpl中正向偏置的漏二极管Dpl(通过Mnl中正向偏置的漏二极管Dn,),从而特别设计成一个大尺寸器件( W/L - 1800/0. 51u_ml)u_m),以承受较高的ESD电平。尽管大尺寸的结电容较大,该电容对模拟端口并没有多大的贡献。所以,模拟端口能够承受一个比较大的ESD电平,但输入电容很小。

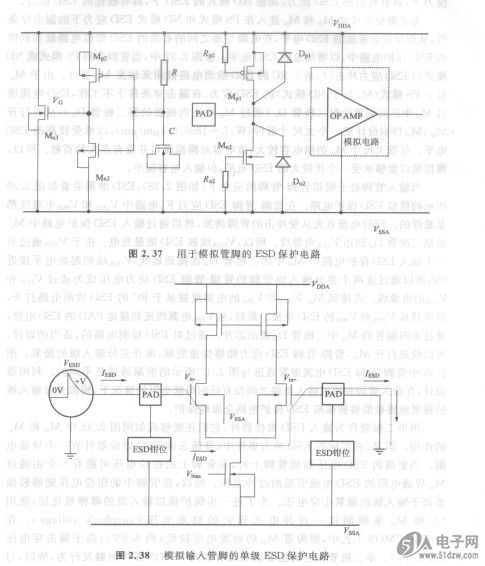

当输入管脚处于模拟管脚一管脚的应力下(如图2. 38),ESD泄漏沿着如图2.39所示的模拟ESD保栌电路。在管脚一管脚ESD应力下,电路中VDDA和SSA电源线都是悬浮的。ESD电流首先从受冲击的管脚诱发,然后通过输入ESD保护电路中M。,的结二极管Dpl到达VDDA电源线。所以,VDDA线被ESD能量充电。由于VDDA通过另一个输入ESD保护电路中M。。中的二极管Dn4连到地线,VDDA线的起始电平接近OV,所以通过这两个差分输入级管脚的管脚一管脚ESD应力电压成为通过VDDA和VSSA的电源线。连接到M。。VDDA和VSSA的电源线被基于RC的ESD检测电路打开,以旁路从V DDA到SSA的ESD电流。最后,从VSSA电源线流到地PAD的ESD电流,通过正向偏置的M。。中二极管Dn4流出芯片。通过对ESD检测电路的,适当的设计,可以快速打开Mn3,管脚一管脚ESD应力能够快速泄漏,离开差分输入级的栅氧。图2. 39中管脚一管脚ESD电流泄漏通道与图2.17所示的泄漏通道是不同的。利用该设计,在输入管脚和模拟输入电路之间没有任何串联电阻的情况下,模拟差分输入级的栅氧能够被能够被模拟ESD保护电路全面地保护。

用单二极管作为输入ESD钳位器件,它们还能够起如同图2.38中的作用。但是,在实际的ESD冲力事件中,导通态的ESD钳位器件有一个导通电阻。当更高的ESD电压加到管脚上时,在管脚上的钳位电压可能有一个由通过导通电阻的ESD电流引起的过冲电压。所以,在管脚中的钳位电压能够轻微地高于输入级的栅氧击穿电压。为了进一步保护模拟输入级的薄栅氧化层,来限制这一过冲电压到它的触发电压( snapback voltage)。在0.35 rumCMOS工艺中,短沟道的触发电压较低(约6.5V),高于漏击穿电压约8. 5V)。单二极管在它的击穿区域没有如同NMOS那样的触发行为,所以,与单二极管相比,有一个安全区域去保护模拟输入级的薄栅氧化层。

用于模拟PAD管脚的ESD保护UC3843电路如图2.37所示,采用0.35 ptm硅化物CMOS单元库的实际版图结构。器件漏区的寄生结电容。为了减少模拟管脚的输入电容,都设计得非常小,其宽长比仅为5010.5(肛m/_um)。在该0.35/um硅化物CMOS工艺中,宽长比为50/0.5(ym/“m)的栎准NMOS管,在PS-模式的ESD的应力下(NMOS管在漏击穿条件下),HBM ESD电平低于500V。但是这样一个小的NMOS管,在同样的0.35Um硅化物CMOS工艺中,能够承8000V的ESD电平,而NMOS管在NS-模式的ESD的应力下(NMOS管在漏二极管正向的条件下)。所以一个NMOS在PS模式和NS模式下,ESD电平相差很大。类似地,一个小尺寸的PMOS管在PD模式的应力下,具有较高的ESD能力,而在ND模式的ESD下,具有较低的ESD能力。

为了避免小尺寸Mn1和Mp1进入在PS模式和ND模式ESD应力下的漏击穿条件,从而导致非常低的ESD电平,在电源与地之间的有效的ESD钳位电路被加到模拟ESD保护电路中,以增加总的ESD电平。在图2.37中,当管脚受到PS模式或ND模式的ESD应力冲击时,基于RC的ESD检测电路被用来触发M。。器件。由于Mp1处于PS模式(Mn1处于ND模式)的ESD应力,在漏击穿条件下不工作,ESD电流通过Mpl中正向偏置的漏二极管Dpl(通过Mnl中正向偏置的漏二极管Dn,),从而特别设计成一个大尺寸器件( W/L - 1800/0. 51u_ml)u_m),以承受较高的ESD电平。尽管大尺寸的结电容较大,该电容对模拟端口并没有多大的贡献。所以,模拟端口能够承受一个比较大的ESD电平,但输入电容很小。

当输入管脚处于模拟管脚一管脚的应力下(如图2. 38),ESD泄漏沿着如图2.39所示的模拟ESD保栌电路。在管脚一管脚ESD应力下,电路中VDDA和SSA电源线都是悬浮的。ESD电流首先从受冲击的管脚诱发,然后通过输入ESD保护电路中M。,的结二极管Dpl到达VDDA电源线。所以,VDDA线被ESD能量充电。由于VDDA通过另一个输入ESD保护电路中M。。中的二极管Dn4连到地线,VDDA线的起始电平接近OV,所以通过这两个差分输入级管脚的管脚一管脚ESD应力电压成为通过VDDA和VSSA的电源线。连接到M。。VDDA和VSSA的电源线被基于RC的ESD检测电路打开,以旁路从V DDA到SSA的ESD电流。最后,从VSSA电源线流到地PAD的ESD电流,通过正向偏置的M。。中二极管Dn4流出芯片。通过对ESD检测电路的,适当的设计,可以快速打开Mn3,管脚一管脚ESD应力能够快速泄漏,离开差分输入级的栅氧。图2. 39中管脚一管脚ESD电流泄漏通道与图2.17所示的泄漏通道是不同的。利用该设计,在输入管脚和模拟输入电路之间没有任何串联电阻的情况下,模拟差分输入级的栅氧能够被能够被模拟ESD保护电路全面地保护。

用单二极管作为输入ESD钳位器件,它们还能够起如同图2.38中的作用。但是,在实际的ESD冲力事件中,导通态的ESD钳位器件有一个导通电阻。当更高的ESD电压加到管脚上时,在管脚上的钳位电压可能有一个由通过导通电阻的ESD电流引起的过冲电压。所以,在管脚中的钳位电压能够轻微地高于输入级的栅氧击穿电压。为了进一步保护模拟输入级的薄栅氧化层,来限制这一过冲电压到它的触发电压( snapback voltage)。在0.35 rumCMOS工艺中,短沟道的触发电压较低(约6.5V),高于漏击穿电压约8. 5V)。单二极管在它的击穿区域没有如同NMOS那样的触发行为,所以,与单二极管相比,有一个安全区域去保护模拟输入级的薄栅氧化层。

上一篇:电流均衡技术

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607