MC74VHCT24AM 支干道红灯亮的状态

发布时间:2019/10/25 21:28:27 访问次数:950

MC74VHCT24AM比较上述交通灯控制系统寄存器传输级和结构级的Verilog描述可知,寄存器传输级描述简单方便,不需要知道电路的具体结构。随着数字系统复杂性的增加,寄存器传输级描述更表现出优越性。

用FPGA器件实现交通灯控制系统

用Altera公司的FLEX10K系列器件EPF10K10LC84-4实现上述设计的过程如下:

在Quartus Ⅱ 5・0软件中建立一个新的工程项目,输入上述HDL文件,对设计项目进行编译:

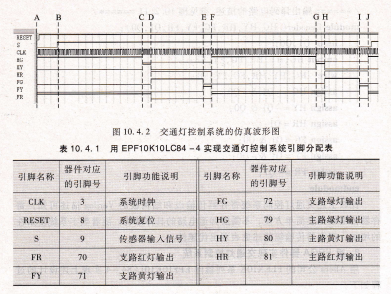

新建一个仿真波形文件,给出输入、输出信号的激励波形,对设计项目进行时序仿真,得到如图10.4.2所示的波形。分析波形图可知,在AB段开始时,低电平有效的RESET信号使系统直接进人主干道绿灯亮、支干道红灯亮的初始状态。BC段表示支干道有车,s=1,并且主干道绿灯需亮足60s,系统转换到CD段,主干道黄灯亮、支干道红灯亮,持续5s后转换到DE段,此时主干道红灯亮、支千道绿灯亮c由于支干道一直有车,DE段持续30s后,系统才进人主干道红灯亮、支干道黄灯亮的EF段,5s后又回到主干道绿灯亮、支干道红灯亮的状态,如图10.4.2中FG段。在主干道红灯亮、支干道绿灯亮的HI段,当支干道没有车s=0时,系统立刻转换到下一个状态,并准各进入主干道绿灯亮、支干道红灯亮的状态。仿真结果完全符合设计要求.

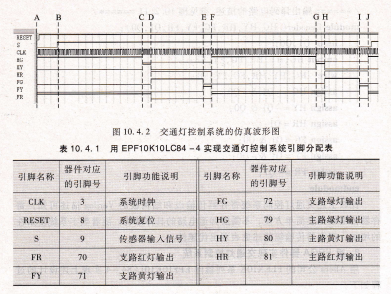

选定目标器件EPF10K10LC84-4,将输人、输出信号分配到器件相应的引脚上,如表10.4.1所示。然后重新编译设计项日,生成下载文件(文件后缀为.pof或.sof)。

将下载文件写入到目标器件中,就是一块专用的交通灯控制电路。寄存器传输级描述对数字密码锁进行寄存器传输级的HDL描述如例10.4.3所示。它分为3

部分,第一部分定义了系统的输人nREsET、TRY、READ、BIT、CLK,输出0PEN、ERROR,所用的寄存器以及系统内部信号变量。第二部分说明了控制单元工作的时序关系。第三部分是处理单元的操作。

根据图10,2.16所示的数字密码锁控制器的ASM图,可以编写出HDL描述。控制单元的HDL描述用两个always语句描述其时序过程。第一个always语句说明异步复位信号RESET使系统进人初态SO,并且系统状态转换是在时钟CLK的上升沿进行的。第二个always语句是由case多路分支语句构成,说明控制单元的5种状态,以及状态之间的转换条件。

第三部分处理单元的HDL编写,可以根据图10.2.15所示的结构图进行。其中第一个always语句说明计数器在控制信号CNT的作用下进行计数,其输出作为选择器的选择信号。当计数器输出为111,即8位密码全部输人.

MC74VHCT24AM比较上述交通灯控制系统寄存器传输级和结构级的Verilog描述可知,寄存器传输级描述简单方便,不需要知道电路的具体结构。随着数字系统复杂性的增加,寄存器传输级描述更表现出优越性。

用FPGA器件实现交通灯控制系统

用Altera公司的FLEX10K系列器件EPF10K10LC84-4实现上述设计的过程如下:

在Quartus Ⅱ 5・0软件中建立一个新的工程项目,输入上述HDL文件,对设计项目进行编译:

新建一个仿真波形文件,给出输入、输出信号的激励波形,对设计项目进行时序仿真,得到如图10.4.2所示的波形。分析波形图可知,在AB段开始时,低电平有效的RESET信号使系统直接进人主干道绿灯亮、支干道红灯亮的初始状态。BC段表示支干道有车,s=1,并且主干道绿灯需亮足60s,系统转换到CD段,主干道黄灯亮、支干道红灯亮,持续5s后转换到DE段,此时主干道红灯亮、支千道绿灯亮c由于支干道一直有车,DE段持续30s后,系统才进人主干道红灯亮、支干道黄灯亮的EF段,5s后又回到主干道绿灯亮、支干道红灯亮的状态,如图10.4.2中FG段。在主干道红灯亮、支干道绿灯亮的HI段,当支干道没有车s=0时,系统立刻转换到下一个状态,并准各进入主干道绿灯亮、支干道红灯亮的状态。仿真结果完全符合设计要求.

选定目标器件EPF10K10LC84-4,将输人、输出信号分配到器件相应的引脚上,如表10.4.1所示。然后重新编译设计项日,生成下载文件(文件后缀为.pof或.sof)。

将下载文件写入到目标器件中,就是一块专用的交通灯控制电路。寄存器传输级描述对数字密码锁进行寄存器传输级的HDL描述如例10.4.3所示。它分为3

部分,第一部分定义了系统的输人nREsET、TRY、READ、BIT、CLK,输出0PEN、ERROR,所用的寄存器以及系统内部信号变量。第二部分说明了控制单元工作的时序关系。第三部分是处理单元的操作。

根据图10,2.16所示的数字密码锁控制器的ASM图,可以编写出HDL描述。控制单元的HDL描述用两个always语句描述其时序过程。第一个always语句说明异步复位信号RESET使系统进人初态SO,并且系统状态转换是在时钟CLK的上升沿进行的。第二个always语句是由case多路分支语句构成,说明控制单元的5种状态,以及状态之间的转换条件。

第三部分处理单元的HDL编写,可以根据图10.2.15所示的结构图进行。其中第一个always语句说明计数器在控制信号CNT的作用下进行计数,其输出作为选择器的选择信号。当计数器输出为111,即8位密码全部输人.

公网安备44030402000607

公网安备44030402000607