优化框体背板时钟匹配电阻的滤波电容

发布时间:2019/1/13 19:47:52 访问次数:509

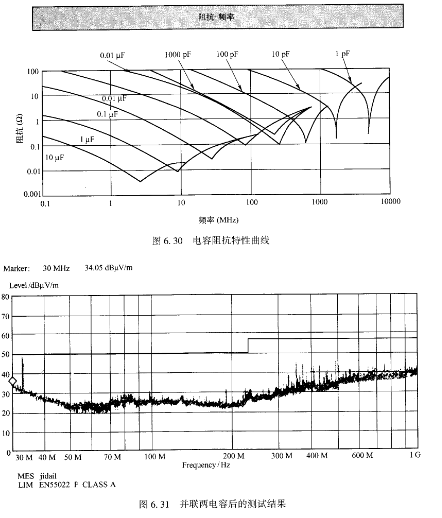

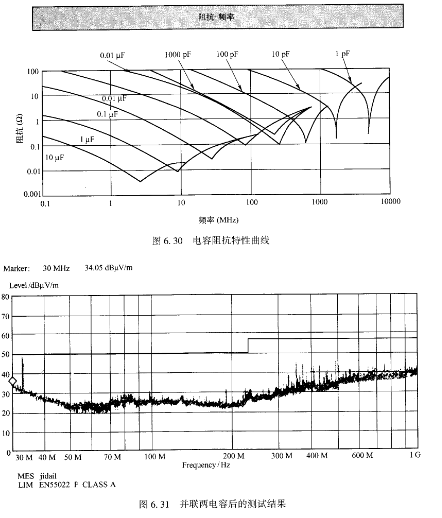

优化框体背板时钟匹配电阻的滤波电容,改为0.1uF和0。⒆2uF。由如图6.30所示的电容阻抗特性曲线可知,两电容并联后的滤波范围在几十兆赫兹之间。 I354SOG修改完后,再进行测试,并联两电容后的测试结果如图6.31所示。

图6.31 并联两电容后的测试结果

图6.31中的测试结果与以前的测试结果相比有改善,说明干扰与ⅤT电源层有关,但是耦合发生在背板还是主控制板,需要进行进一步的定位。

利用专门加工的接插件将主控制板输出的32.768MHz时钟上拉到Ⅴm,然后启动主控制板,通过接插件上拉的原理图如图6.32所示。

通过接插件上拉后再进行测试,结果如图6.33所示。

图633 通过接插件上拉后的测试频谱图

再在电源线上套上磁环后进行测试,得到如图6.34所示的结果。

优化框体背板时钟匹配电阻的滤波电容,改为0.1uF和0。⒆2uF。由如图6.30所示的电容阻抗特性曲线可知,两电容并联后的滤波范围在几十兆赫兹之间。 I354SOG修改完后,再进行测试,并联两电容后的测试结果如图6.31所示。

图6.31 并联两电容后的测试结果

图6.31中的测试结果与以前的测试结果相比有改善,说明干扰与ⅤT电源层有关,但是耦合发生在背板还是主控制板,需要进行进一步的定位。

利用专门加工的接插件将主控制板输出的32.768MHz时钟上拉到Ⅴm,然后启动主控制板,通过接插件上拉的原理图如图6.32所示。

通过接插件上拉后再进行测试,结果如图6.33所示。

图633 通过接插件上拉后的测试频谱图

再在电源线上套上磁环后进行测试,得到如图6.34所示的结果。

上一篇:VTT通过外部供电

热门点击

热门点击

- MAX3232ESE是工业级芯片

- JR36系列热继电器

- 用继电器控制电热丝的通/断

- 传导抗扰度测试目的

- 在电源的输出端口上串联一个150uH的共模电

- 光耦两端的数字地与模拟地如何接

- 电场天线可以与电容相关联

- TX、RX信号线上进行滤波

- 解决电源线辐射的最直接措施就是在电源端口上加

- 电感、电阻、电容、导线本身并不是保护器件

推荐技术资料

推荐技术资料

- 单片机版光立方的制作

- N视频: http://v.youku.comN_sh... [详细]

公网安备44030402000607

公网安备44030402000607