应力记忆技术的刻蚀

发布时间:2017/11/5 17:01:14 访问次数:1208

应力记忆技术(sMT)L2Γ已经成为应变硅技术的一种,从65nm△艺节点开始用于增强NMOs的性能。 PCI2050BIZHK通常将具有拉伸应力的SiN层覆盖在NMC)S上,在尖峰退火后便产生了SMT效应。由于多晶硅和⒏N层导热系数的差异,在尖峰退火中产生了一个面内拉伸应力和一个纵向压缩应力,并将其直接传递到沟道中。NMOS的性能将受益于这种组合的应变形式,应力的强度与应力薄膜的密度(杨氏模量)直接相关。通常,低密度/孑L隙率意味着有较大的应力被引人到了多晶硅栅中。然而,在sMT应用的早期阶段,NMOs性能的提升是以PMOS性能下降为代价的。由于有⒏N层覆盖,氧化物下面的氢无法在尖峰退火时释放掉,最终造成PMOS源区和漏区的硼失去活性和外扩。这种PMOS性能的退化与SiN应力层的孔隙率密切相关,并会随着siN薄膜孔隙率的增加完全消除。然而,这不是NMOS特性所需要的。NM()s特性需要siN薄膜具有更小的孔隙率,以此来引人高应力。

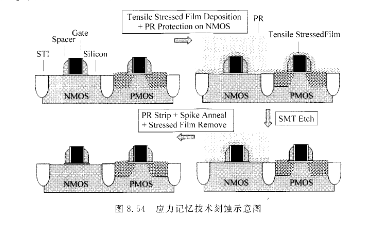

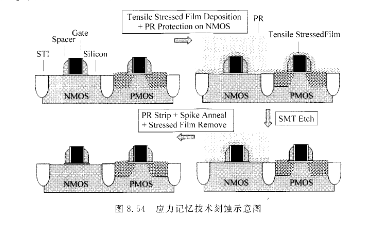

图8,54显示的是避免PMOS退化的解决方案之一.即在尖峰退火前,通过干法刻蚀(SMT刻蚀),局部除去应力薄膜。通常的做法是在SiN应力薄膜下面,先生长一层薄氧化层作为停止层。SMT刻蚀主要包含两个步骤:①采用低压((20mTorr)和CF!的短时间主刻蚀;②采用CHF3和CH2F2的高选择比过刻蚀。SMT刻蚀可以在导体刻蚀机中进行,剩下的SiN覆盖层最后用湿法除去。SMT刻蚀屮的一个问题是SiN层厚在图形稠密和疏松区域之间的变化。随着CMOS的等比例缩小,这个问题变得尤为糟糕。因为在小问距的情况下,更薄的siN薄膜常常与穿通的风险以及sGe损失所造成的PM()s退化有关。sN应力层与其停止层之间的高刻蚀选择比是至关重要的,其引发了对不同薄停止层的评

估。除了11面的SMT刻蚀以外,由于存在于SMT相关的窄宽度效应,所以可能对NMOs上的⒏N层需要-种新的SMT刻蚀。也就是说,在NMC)s屮,可以基于AA(activc area)的宽度调节引入的应力。

应力记忆技术(sMT)L2Γ已经成为应变硅技术的一种,从65nm△艺节点开始用于增强NMOs的性能。 PCI2050BIZHK通常将具有拉伸应力的SiN层覆盖在NMC)S上,在尖峰退火后便产生了SMT效应。由于多晶硅和⒏N层导热系数的差异,在尖峰退火中产生了一个面内拉伸应力和一个纵向压缩应力,并将其直接传递到沟道中。NMOS的性能将受益于这种组合的应变形式,应力的强度与应力薄膜的密度(杨氏模量)直接相关。通常,低密度/孑L隙率意味着有较大的应力被引人到了多晶硅栅中。然而,在sMT应用的早期阶段,NMOs性能的提升是以PMOS性能下降为代价的。由于有⒏N层覆盖,氧化物下面的氢无法在尖峰退火时释放掉,最终造成PMOS源区和漏区的硼失去活性和外扩。这种PMOS性能的退化与SiN应力层的孔隙率密切相关,并会随着siN薄膜孔隙率的增加完全消除。然而,这不是NMOS特性所需要的。NM()s特性需要siN薄膜具有更小的孔隙率,以此来引人高应力。

图8,54显示的是避免PMOS退化的解决方案之一.即在尖峰退火前,通过干法刻蚀(SMT刻蚀),局部除去应力薄膜。通常的做法是在SiN应力薄膜下面,先生长一层薄氧化层作为停止层。SMT刻蚀主要包含两个步骤:①采用低压((20mTorr)和CF!的短时间主刻蚀;②采用CHF3和CH2F2的高选择比过刻蚀。SMT刻蚀可以在导体刻蚀机中进行,剩下的SiN覆盖层最后用湿法除去。SMT刻蚀屮的一个问题是SiN层厚在图形稠密和疏松区域之间的变化。随着CMOS的等比例缩小,这个问题变得尤为糟糕。因为在小问距的情况下,更薄的siN薄膜常常与穿通的风险以及sGe损失所造成的PM()s退化有关。sN应力层与其停止层之间的高刻蚀选择比是至关重要的,其引发了对不同薄停止层的评

估。除了11面的SMT刻蚀以外,由于存在于SMT相关的窄宽度效应,所以可能对NMOs上的⒏N层需要-种新的SMT刻蚀。也就是说,在NMC)s屮,可以基于AA(activc area)的宽度调节引入的应力。

公网安备44030402000607

公网安备44030402000607