高密度等离子体化学气相沉积工艺

发布时间:2017/10/18 21:06:10 访问次数:1354

在HDP CVD工艺问世之前,大多数 NCP5661DT33RKG芯片厂普遍采用等离子体增强化学气相沉积(PE CVD)进行绝缘介质的填充。这种工艺对于大于0.8um的间隔具有良好的填孔效果,然而对于小于0.8um的间隔,用P:CVD工艺一步填充这么高的深宽比(定义为间隙的深度和宽度的比值)的间隔时会在间隔中部产生夹断(pincl△off)和空穴(见图4.12)。其他一些传统CVD工艺,如常压CVD(APCVD)和亚常压CVD(SACVD)虽然可以提供对小至0.25um的间隔的无孔填充,但这些缺乏等离子体辅助沉积产生的膜会有低密度和吸潮性等缺点,需要增加P:CVD薄膜对其进行保护,或者进行后沉积处理(如退火回流等)。这些工序的加人同样提高了生产成本,增加了整个I艺流程的步骤和复杂性。

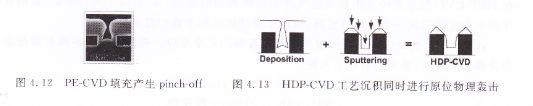

为了同时满足高深宽比间隙的填充和控制生产成本,诞生了HDP CVD工艺,它的特点在于,可以在同一个反应腔中同步地进行沉积和物理轰击(见图4.13),从而实现绝缘介质在沟槽中的bottom up生长。

在HDP CVD工艺问世之前,大多数 NCP5661DT33RKG芯片厂普遍采用等离子体增强化学气相沉积(PE CVD)进行绝缘介质的填充。这种工艺对于大于0.8um的间隔具有良好的填孔效果,然而对于小于0.8um的间隔,用P:CVD工艺一步填充这么高的深宽比(定义为间隙的深度和宽度的比值)的间隔时会在间隔中部产生夹断(pincl△off)和空穴(见图4.12)。其他一些传统CVD工艺,如常压CVD(APCVD)和亚常压CVD(SACVD)虽然可以提供对小至0.25um的间隔的无孔填充,但这些缺乏等离子体辅助沉积产生的膜会有低密度和吸潮性等缺点,需要增加P:CVD薄膜对其进行保护,或者进行后沉积处理(如退火回流等)。这些工序的加人同样提高了生产成本,增加了整个I艺流程的步骤和复杂性。

为了同时满足高深宽比间隙的填充和控制生产成本,诞生了HDP CVD工艺,它的特点在于,可以在同一个反应腔中同步地进行沉积和物理轰击(见图4.13),从而实现绝缘介质在沟槽中的bottom up生长。

上一篇:半导体绝缘介质的填充

上一篇:HDP-CVD作用机理

热门点击

热门点击

- CVD是用来制备二氧化硅介质薄膜的主要工艺方

- 电子产品装配过程中常用的图纸有哪些?

- 载流子迁移率提高技术

- W plugR制程

- 薄层金属沉积需要良好的台阶覆盖性

- 天线距离地平面的高度应在规定的范围内变化

- 电流返回的最低阻抗通道并非是最短路径高

- HDP-CⅤD常见反应

- 为避免高频信号通过PCB走线时产生电磁辐射

- 高密度等离子体化学气相沉积工艺

推荐技术资料

推荐技术资料

- 业余条件下PCM2702

- PGM2702采用SSOP28封装,引脚小而密,EP3... [详细]

公网安备44030402000607

公网安备44030402000607