部分译码法

发布时间:2014/6/3 20:48:34 访问次数:6531

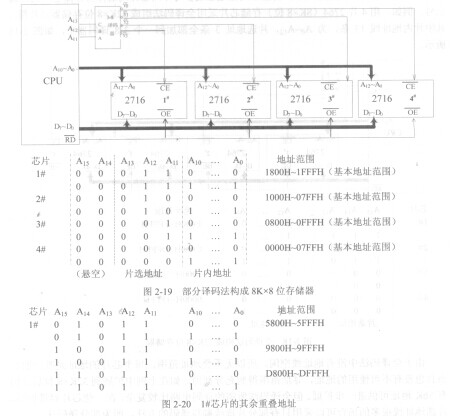

部分译码法是指用CPU的部分高位地址线参与译码后作为存储芯片的片选信号。它是SN74HC165DR线选法写全译码法的一个折中,一方面可以简化译码器的设计,另一方面有较强的存储器容量扩展能力和连续的存储器范围。例如,用4片2716扩展存储器的容量,如图2-19所示。

图2-19中采用3条高位地址线A13~All加到一个3-8译码器的输入端,选用其中的4条输出作为4块芯片的片选信号。此时,为了确定每片芯片的地址范围,悬空没用到的高位地址( Ais、A14)可假设为“0”,这样确定出来的地址与线选法中的一样,都称为“基

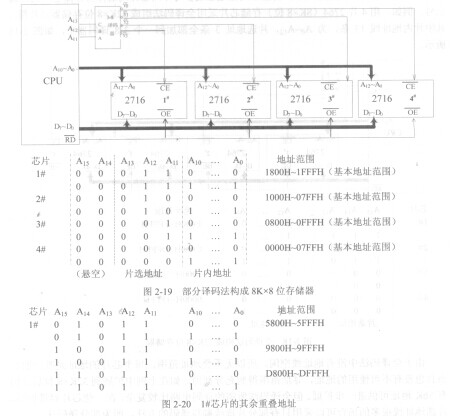

本地址”,确定的方法不变。同样,部分译码法也存在重叠地址,而且重叠地址的个数m与悬空地址线的条数n的关系为:m=2“,在本例中每片芯片共有4个重叠地址(其中一个为基本地址),分别假设当A15A14=01、10和11时,其余的地址确定方法不变。例如,14芯片的其余重叠地址如图2-20所示。

图2-20 芯片的其余重叠地址

用同样的方法,不难写出其余芯片的重叠地址。部分译码法的连接方案中,由于地址重叠,影响了地址区的有效使用,也限制了存储器的扩展。因此,在选用部分译码时,也要尽可能多选一些高位地址线来作为译码器的输入。

部分译码法是指用CPU的部分高位地址线参与译码后作为存储芯片的片选信号。它是SN74HC165DR线选法写全译码法的一个折中,一方面可以简化译码器的设计,另一方面有较强的存储器容量扩展能力和连续的存储器范围。例如,用4片2716扩展存储器的容量,如图2-19所示。

图2-19中采用3条高位地址线A13~All加到一个3-8译码器的输入端,选用其中的4条输出作为4块芯片的片选信号。此时,为了确定每片芯片的地址范围,悬空没用到的高位地址( Ais、A14)可假设为“0”,这样确定出来的地址与线选法中的一样,都称为“基

本地址”,确定的方法不变。同样,部分译码法也存在重叠地址,而且重叠地址的个数m与悬空地址线的条数n的关系为:m=2“,在本例中每片芯片共有4个重叠地址(其中一个为基本地址),分别假设当A15A14=01、10和11时,其余的地址确定方法不变。例如,14芯片的其余重叠地址如图2-20所示。

图2-20 芯片的其余重叠地址

用同样的方法,不难写出其余芯片的重叠地址。部分译码法的连接方案中,由于地址重叠,影响了地址区的有效使用,也限制了存储器的扩展。因此,在选用部分译码时,也要尽可能多选一些高位地址线来作为译码器的输入。

上一篇:全译码法

上一篇:存储器字数和位数的扩展

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607