全译码法

发布时间:2014/6/3 20:46:07 访问次数:7906

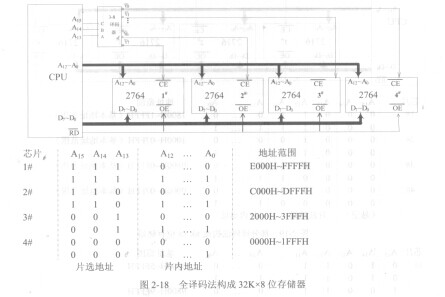

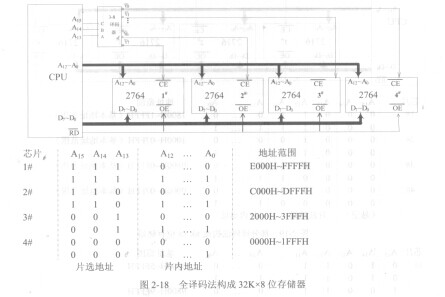

全译码法的特点是使用CPU的全部高位地址线参与译码器译码后作为存储芯片的片选信号。SN74HC164DR例如,用4片2764(8Kx8位)存储芯片采用全译码法组成32Kx8位存储器芯片组,其中片内地址线13条,为AO~A12,片选地址3条全部加到一个3-8译码器上,如图2-18所示。

图2-18全译码法构成32Kx8位存储器

由于全译码法中没有地址线空闲,所以无重叠地址范围,每个芯片的地址是唯一的。而且也没有不可使用的地址,寻址范围得到充分利用。如在上例中扩展到32Kx8位后,仍有56K地址可供进一步扩展。但全译码法所需的译码电路比较复杂,在一些芯片容量很小,片选地址线很多的场合可以采用只有部分片选线参与译码的方法,即为部分译码法。

全译码法的特点是使用CPU的全部高位地址线参与译码器译码后作为存储芯片的片选信号。SN74HC164DR例如,用4片2764(8Kx8位)存储芯片采用全译码法组成32Kx8位存储器芯片组,其中片内地址线13条,为AO~A12,片选地址3条全部加到一个3-8译码器上,如图2-18所示。

图2-18全译码法构成32Kx8位存储器

由于全译码法中没有地址线空闲,所以无重叠地址范围,每个芯片的地址是唯一的。而且也没有不可使用的地址,寻址范围得到充分利用。如在上例中扩展到32Kx8位后,仍有56K地址可供进一步扩展。但全译码法所需的译码电路比较复杂,在一些芯片容量很小,片选地址线很多的场合可以采用只有部分片选线参与译码的方法,即为部分译码法。

上一篇:6264芯片的地址范围

上一篇:部分译码法

公网安备44030402000607

公网安备44030402000607