数字电路接地噪声

发布时间:2014/4/16 20:07:51 访问次数:851

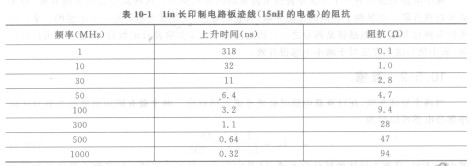

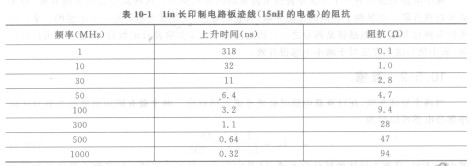

瞬态接地电流是产生系统内部噪声电压、传导和辐射发射的主要原因。为了减小来自瞬态接地电流的噪声,CD4047BM96必须把接地阻抗减到最小。一个典型的印制电路板( PCB)的迹线(loz的铜导线0. 006in宽,距返回导线0.02in)具有82mQ厂in的电阻(式(5-10》,和15nH/in的回路电感(式(10-5》。表10-1表示15nH的电感阻抗随频率变化,与式(10-2)所确定的逻辑电路上升/下降时间有关。

表10-1 lin长印制电路板迹线(15nH的电感)的阻抗

可以看出,当频率高于1MHz,15nH电感的阻抗大于82mfl的电阻。频率高于ldiVIHz,电感比该电阻大几个数量级。对于具有Ins上升时间(由式(10-2)可知带宽为318MHz)的数字信号而言,接地导体将具有约30Q/in的感抗。因而,在设计数字印制线路板时,电感是考虑的重点。如果要使接地电路阻抗最小,则电感减小一个数量级或更多。

瞬态接地电流是产生系统内部噪声电压、传导和辐射发射的主要原因。为了减小来自瞬态接地电流的噪声,CD4047BM96必须把接地阻抗减到最小。一个典型的印制电路板( PCB)的迹线(loz的铜导线0. 006in宽,距返回导线0.02in)具有82mQ厂in的电阻(式(5-10》,和15nH/in的回路电感(式(10-5》。表10-1表示15nH的电感阻抗随频率变化,与式(10-2)所确定的逻辑电路上升/下降时间有关。

表10-1 lin长印制电路板迹线(15nH的电感)的阻抗

可以看出,当频率高于1MHz,15nH电感的阻抗大于82mfl的电阻。频率高于ldiVIHz,电感比该电阻大几个数量级。对于具有Ins上升时间(由式(10-2)可知带宽为318MHz)的数字信号而言,接地导体将具有约30Q/in的感抗。因而,在设计数字印制线路板时,电感是考虑的重点。如果要使接地电路阻抗最小,则电感减小一个数量级或更多。

上一篇:有极性输出毫话的CMOS逻辑门

上一篇:实用的数字电路接地系统

公网安备44030402000607

公网安备44030402000607