电子管接普通负载

发布时间:2013/7/11 19:47:22 访问次数:1493

对于电子管接普通负载812H-1A-C-24V的情形来说,Va升高时下降,电子管向截止状态靠近,我们还必须依据电子管特性曲线簇考虑由此带来的限制。但现在,接的是恒流源负载,保持不变,需考虑的限制仅限于恒流源是否有足够的压降来保证自身的正常工作。就级联式恒流源而言,15V的压降已十分充足,因此,采用400V的HT电源电压时,可允许Va摆动至385V。再根据8mA负线与栅极电压的对应情况来判断,很可能从Va~lOOV开始,就会有栅极电流出现。因此,最大的可用输出摆幅是38 5V-1 00V=28 SVpk-pIC-100 VRMS。

尽管通过恒流源的强迫作用,使电子管的工作电流设定为/a=8mA,但我们还必须通过调整电子管的偏置来设定虼。在刚出现削波的时候,为得到最大的可用输出摆幅,电子管输出波形应当是正半周与负半周同时开始削波,因此,电子管的工作点应设置在阳极电压最高点( Vmax.)与最低点(Vmin.)之间的中点――也就是取平均值:

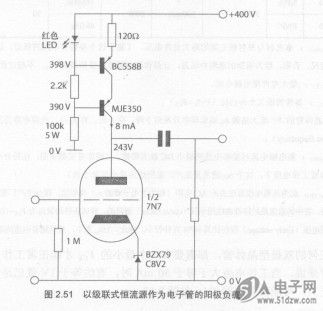

再看电子管的特性曲线簇,可以看到,要获得这个Va值,需要设置Vgk~8V(译注:原文为Vgk~8V)。而这可以通过一只8.2V齐纳二极管来实现。电路见图2.51。

由于这一电路主要用于处理大信号电压,因此,噪声方面不会成为问题。齐纳二极管就没有必要并联一只旁路电容。

在这个电路里,如果电子管的两端电压确实有242.5V,那么,处于恒流源下方的晶体管将有142.5V的压降,其静态功耗达到1.18W。如果Va摆动到100V,这只晶体管将承受285V的电压,此时的工作电流仞为8mA,因此,瞬时功耗为2.28W。这个数值(2.28W),看起来像是对晶体管额定功耗的最低要求。但实际上,由于输出正向摆幅与负向摆幅相等,所以,一个完整信号周期内的晶体管平均功耗,仍等于之前计算出来的静态功耗( 1.18W)。

对于电子管接普通负载812H-1A-C-24V的情形来说,Va升高时下降,电子管向截止状态靠近,我们还必须依据电子管特性曲线簇考虑由此带来的限制。但现在,接的是恒流源负载,保持不变,需考虑的限制仅限于恒流源是否有足够的压降来保证自身的正常工作。就级联式恒流源而言,15V的压降已十分充足,因此,采用400V的HT电源电压时,可允许Va摆动至385V。再根据8mA负线与栅极电压的对应情况来判断,很可能从Va~lOOV开始,就会有栅极电流出现。因此,最大的可用输出摆幅是38 5V-1 00V=28 SVpk-pIC-100 VRMS。

尽管通过恒流源的强迫作用,使电子管的工作电流设定为/a=8mA,但我们还必须通过调整电子管的偏置来设定虼。在刚出现削波的时候,为得到最大的可用输出摆幅,电子管输出波形应当是正半周与负半周同时开始削波,因此,电子管的工作点应设置在阳极电压最高点( Vmax.)与最低点(Vmin.)之间的中点――也就是取平均值:

再看电子管的特性曲线簇,可以看到,要获得这个Va值,需要设置Vgk~8V(译注:原文为Vgk~8V)。而这可以通过一只8.2V齐纳二极管来实现。电路见图2.51。

由于这一电路主要用于处理大信号电压,因此,噪声方面不会成为问题。齐纳二极管就没有必要并联一只旁路电容。

在这个电路里,如果电子管的两端电压确实有242.5V,那么,处于恒流源下方的晶体管将有142.5V的压降,其静态功耗达到1.18W。如果Va摆动到100V,这只晶体管将承受285V的电压,此时的工作电流仞为8mA,因此,瞬时功耗为2.28W。这个数值(2.28W),看起来像是对晶体管额定功耗的最低要求。但实际上,由于输出正向摆幅与负向摆幅相等,所以,一个完整信号周期内的晶体管平均功耗,仍等于之前计算出来的静态功耗( 1.18W)。

上一篇:晶体管恒流源用作电子管的有源负载

上一篇:采用集成块LM3342的恒流源

热门点击

热门点击

- 容抗、感抗与频率的关系

- SRPP电路工作点的选定

- 散热片的安装

- 集成电路TA7630P引脚作用

- 双极晶体管的IC-VBE特性

- 束射四极管与五极管

- 输出耦合电容值的选取

- 反馈公式

- VD2和VD3两只整流二极管导通时的电流回路

- 采用开关集成电路和继电器构成的扬声器保护电路

推荐技术资料

推荐技术资料

- 自制智能型ICL7135

- 表头使ff11CL7135作为ADC,ICL7135是... [详细]

公网安备44030402000607

公网安备44030402000607