晶体管恒流源用作电子管的有源负载

发布时间:2013/7/11 19:44:42 访问次数:4318

对于前面介绍的所有晶体812-2A-C-24V管恒流源电路,将NPN管换为PNP管后,以OV线为基准,都可以镜像成另一种极性的恒流源电路。然后,将之与HT电源线相接,可以充当电子管的有源负载。在这样的接法下,真空三极管可以充分发挥其放大能力,获得的效果。更为重要的是,即使电子管工作在较低的HT电压下,仍可具备良好的失真性能。

以ECC83这种常见的高∥值电子管来举例。为避免出现栅流,ECC83需要有相当高的Va电压,典型值为150V。一般情况下,需要做到RL>2r。,而ECC83有ra~75kQ。因此,我们可以选定,RL=150kQ,并设置成/a=0.7mA,因此,RL上将有105V的压降。我们需要使用225V的HT电源电压。实际上,我们或许只要求电路输出的摆幅能达到SVpk-pk即可,这样一来,大部分的HT电压被浪费了。如果我们用晶体管恒流源取代150kQ电阻,电子管就会得到阻值高得多的RL,而且,

我们还可以按照最大输出摆幅的要求,来选定HT电源电压。电路如图2.49所示。

图2.49中的电路,就是采用了上述的设计理念。其设计的起因,主要是作者需要用到一个高增益的差分对电路( ECC83:p=100),而HT正电源仅能提供150V的供电电压。请注意,所采用的晶体管是高耐压型号,因为要求它必须能应付电子管阳极摆动至OV时的情况。

通常情况下,为降低噪声,齐纳二极管需要并联旁路电容。在这里,由于两炅齐纳二极管产生的噪声是共模信号,能够被下一级电路(也是差分对电路)所抑制,所以就不设旁路电容。经测试,此电路在输出7Vpk_pk的摆幅下,lkH的失真仅有0.04%。

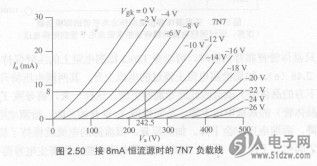

使用级联式恒流源作为有源负载,可以大大提升,。ut,并且能拉平负载线、减小电子管的失真。如果我们想同时获得最大输出摆幅、最小失真,我们可以选用7N7(6SN7的锁式管座版本),并选定/a=8mA,因为当/a>6mA,其∥值更接近于保持不变。假设级联式恒流源能提供呈水平的负载线,我们可以利用8mA这个点画出负载线来,见图2.50。

对于前面介绍的所有晶体812-2A-C-24V管恒流源电路,将NPN管换为PNP管后,以OV线为基准,都可以镜像成另一种极性的恒流源电路。然后,将之与HT电源线相接,可以充当电子管的有源负载。在这样的接法下,真空三极管可以充分发挥其放大能力,获得的效果。更为重要的是,即使电子管工作在较低的HT电压下,仍可具备良好的失真性能。

以ECC83这种常见的高∥值电子管来举例。为避免出现栅流,ECC83需要有相当高的Va电压,典型值为150V。一般情况下,需要做到RL>2r。,而ECC83有ra~75kQ。因此,我们可以选定,RL=150kQ,并设置成/a=0.7mA,因此,RL上将有105V的压降。我们需要使用225V的HT电源电压。实际上,我们或许只要求电路输出的摆幅能达到SVpk-pk即可,这样一来,大部分的HT电压被浪费了。如果我们用晶体管恒流源取代150kQ电阻,电子管就会得到阻值高得多的RL,而且,

我们还可以按照最大输出摆幅的要求,来选定HT电源电压。电路如图2.49所示。

图2.49中的电路,就是采用了上述的设计理念。其设计的起因,主要是作者需要用到一个高增益的差分对电路( ECC83:p=100),而HT正电源仅能提供150V的供电电压。请注意,所采用的晶体管是高耐压型号,因为要求它必须能应付电子管阳极摆动至OV时的情况。

通常情况下,为降低噪声,齐纳二极管需要并联旁路电容。在这里,由于两炅齐纳二极管产生的噪声是共模信号,能够被下一级电路(也是差分对电路)所抑制,所以就不设旁路电容。经测试,此电路在输出7Vpk_pk的摆幅下,lkH的失真仅有0.04%。

使用级联式恒流源作为有源负载,可以大大提升,。ut,并且能拉平负载线、减小电子管的失真。如果我们想同时获得最大输出摆幅、最小失真,我们可以选用7N7(6SN7的锁式管座版本),并选定/a=8mA,因为当/a>6mA,其∥值更接近于保持不变。假设级联式恒流源能提供呈水平的负载线,我们可以利用8mA这个点画出负载线来,见图2.50。

上一篇:电子管接普通负载

公网安备44030402000607

公网安备44030402000607