并行进位同步二进制加法计数器

发布时间:2012/12/10 19:26:04 访问次数:2607

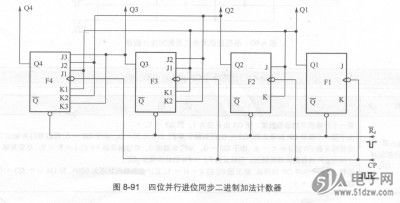

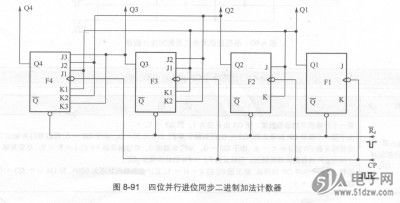

图8-91所示是由4个JK触发器构成的EP2S30F484C5四位并行进位同步二进制加法计数器,这一电路与前一个串行同步计数器电路相比有一点不同之处,就是电路中的JK触发器有多个J和K输入端,如触发器F3有2个这样的输入端,触发器F4则有3个J、K输入端。

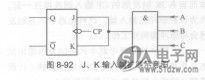

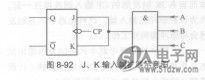

Jl、J2和J3是一个与门电路的3个输入端,Kl、K2和K3是一个与门电路的3个输入端。如果JK触发器的J、K输入端数目不够用时,可使用附加的与门电路来扩展,如图8-92所示。图8-92 J、K输入端扩展示意图。

对于并行进位同步二进制加法计数器,计数前先清零,即在Rd端加上负脉冲,这样计数器输出状态为0000,即Q4=O,Q3=0,Q2=0,Ql=O。下面根据输入计数脉冲CP分成几种情况分析这一电路的加法计数过程。

通过上述分析可知,计数脉冲CP是同时加到各JK触发器的CP端,进位信号是通过本级的多个J、K输入端实现的,各触发器的进位信号是并行的,这种计数方式称为并行同步计数。

图8-91所示是由4个JK触发器构成的EP2S30F484C5四位并行进位同步二进制加法计数器,这一电路与前一个串行同步计数器电路相比有一点不同之处,就是电路中的JK触发器有多个J和K输入端,如触发器F3有2个这样的输入端,触发器F4则有3个J、K输入端。

Jl、J2和J3是一个与门电路的3个输入端,Kl、K2和K3是一个与门电路的3个输入端。如果JK触发器的J、K输入端数目不够用时,可使用附加的与门电路来扩展,如图8-92所示。图8-92 J、K输入端扩展示意图。

对于并行进位同步二进制加法计数器,计数前先清零,即在Rd端加上负脉冲,这样计数器输出状态为0000,即Q4=O,Q3=0,Q2=0,Ql=O。下面根据输入计数脉冲CP分成几种情况分析这一电路的加法计数过程。

通过上述分析可知,计数脉冲CP是同时加到各JK触发器的CP端,进位信号是通过本级的多个J、K输入端实现的,各触发器的进位信号是并行的,这种计数方式称为并行同步计数。

上一篇:串行进位同步二进制加法计数器

上一篇:同步二进制可逆计数器

公网安备44030402000607

公网安备44030402000607