单稳态触发器

发布时间:2012/9/16 15:52:29 访问次数:2050

五、十进制加法计数器74LS90构成电W.FL-R-SMT-1(10)子秒表的计数单元,如图6.53中单元Ⅳ所示。其中计数器①接成五进制形式,对频率为50 Hz的时钟脉冲进行五分频,在输出端Q。取得周期为0.1s的矩形脉冲,作为计数器②的时钟输入。计数器2及计数器3接成8421码十进制形式,其输出端与实验装置上译码显示单元的相应输入端连接,可显示0.1~0.9s、1―9.9s计时。

最后介绍一下集成异步计数器74LS90。

74LS90是异步二、五、十进制加法计数器,它既可以作二进制加法计数器,又可以作五进制和十进制加法计数器。

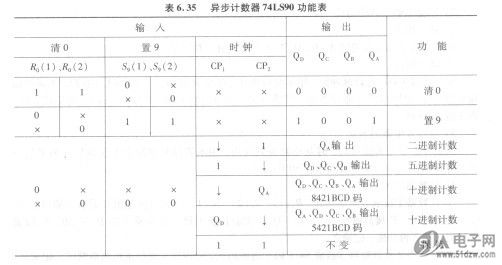

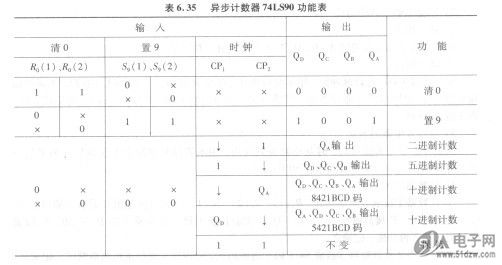

图6.55为74LS90引脚排列,表6.35为功能表。

通过不同的连接方式,74LS90可以实现四种不同的逻辑功能;而且还可借助R。(1)、Ro (2)对计数器清零,借助S9(1)、S9 (2)将计数器置9。其具体功能详述如下:

①计数脉冲从CP,输入,Q。作为输出端,为二进制计数器。

②计数脉冲从CP:输入,Q。、Qc、Q。作为输出端,为异步五进制加法计数器。

③若将CP:和Q。相连,计数脉冲由CP.输入,Q。、Q。、Q。、Q。作为输出端,则构成异步8421码’卜进制加法计数器。

④若将CP,与Q。相连,计数脉冲由CP:输入,Q。、Q。、Q。、Q。作为输出端,则构成异步5421码十进制加法计数器。

⑤清零、置9功能。

a.异步清零

当R。(1)、R。(2)均为“1”;S。(1)、Js。(2)中有“0”时,实现异步清零功能,即QDQcQBQA =0000。

b.置9功能

当S。(1)、S。(2)均为“l”;Ro (1)、R。(2)中有“O”时,实现置9功能,即QDQcQBQA=1001。

五、十进制加法计数器74LS90构成电W.FL-R-SMT-1(10)子秒表的计数单元,如图6.53中单元Ⅳ所示。其中计数器①接成五进制形式,对频率为50 Hz的时钟脉冲进行五分频,在输出端Q。取得周期为0.1s的矩形脉冲,作为计数器②的时钟输入。计数器2及计数器3接成8421码十进制形式,其输出端与实验装置上译码显示单元的相应输入端连接,可显示0.1~0.9s、1―9.9s计时。

最后介绍一下集成异步计数器74LS90。

74LS90是异步二、五、十进制加法计数器,它既可以作二进制加法计数器,又可以作五进制和十进制加法计数器。

图6.55为74LS90引脚排列,表6.35为功能表。

通过不同的连接方式,74LS90可以实现四种不同的逻辑功能;而且还可借助R。(1)、Ro (2)对计数器清零,借助S9(1)、S9 (2)将计数器置9。其具体功能详述如下:

①计数脉冲从CP,输入,Q。作为输出端,为二进制计数器。

②计数脉冲从CP:输入,Q。、Qc、Q。作为输出端,为异步五进制加法计数器。

③若将CP:和Q。相连,计数脉冲由CP.输入,Q。、Q。、Q。、Q。作为输出端,则构成异步8421码’卜进制加法计数器。

④若将CP,与Q。相连,计数脉冲由CP:输入,Q。、Q。、Q。、Q。作为输出端,则构成异步5421码十进制加法计数器。

⑤清零、置9功能。

a.异步清零

当R。(1)、R。(2)均为“1”;S。(1)、Js。(2)中有“0”时,实现异步清零功能,即QDQcQBQA =0000。

b.置9功能

当S。(1)、S。(2)均为“l”;Ro (1)、R。(2)中有“O”时,实现置9功能,即QDQcQBQA=1001。

热门点击

热门点击

- 放大倍数是跨导gM

- RLC串联电路的谐振特性

- 线性有源二端网络等效参数测量

- 方波一三角波发生器设计与研究(设计性实验)

- 乒乓球模拟比赛(综合性实验)

- 关键工序和特殊工序的控制

- 电路图的基本知识

- 连接导线的中断画法规则

- 单稳态触发器

- 观察正弦波信号通过电路时产生的延迟和畸变

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607