共发射极放大器的NPN晶体管

发布时间:2020/9/20 0:51:24 访问次数:2138

共发射极放大器是三种基本单级放大器拓扑之一。BJT共发射极放大器一般用作反相电压放大器。晶体管的基极端为输入,集电极端为输出,而发射极为输入和输出共用(可连接至参考地端或电源轨),所谓“共射”即由此而来。

材料

ADALM2000主动学习模块

无焊面包板

五个电阻

一个50 kΩ可变电阻、电位计

一个小信号NPN晶体管(2N3904)

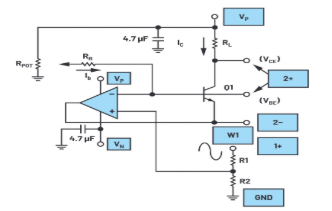

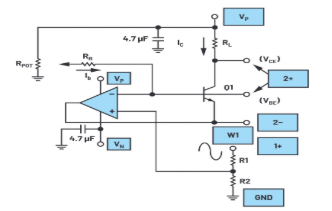

配置展现了用作共发射极放大器的NPN晶体管。选择适当的输出负载电阻RL,用于产生合适的标称集电极电流IC,VCE电压约为VP (5 V)的一半。通过可调电阻RPOT与RB来设置晶体管(IB)的标称偏置工作点,进而设置所需的IC。选择适当的分压器R1/R2,以便通过波形发生器W1提供足够大的输入激励衰减。考虑到在晶体管VBE的基极上会出现非常小的信号,这样做更容易查看发生器W1信号。衰减波形发生器W1信号通过4.7 uF电容交流耦合到晶体管基极,以免干扰直流偏置条件。

Q波段采用对脊鳍线微带过渡结构的5 W固态集成功率放大模块。利用HFSS软件对四路波导T型节以及对脊鳍线微带过渡结构分别进行模拟仿真,仿真结果表明,四路波导T型节插入损耗可以控制在0.1 dB以内,对脊鳍线微带过渡结构插入损耗可以控制在0.1 dB以内。对四路合成/分配器进行背对背安装,并进行直通测试,测试结果表明,在43.5 GHz~45.5 GHz频段内插入损耗在2 dB以内,可以推算合成效率大于80%。选用2 W的功放MMIC作为实验样片进行装配,采用金丝键的方式进行射频连接。对整个功率放大模块进行测试,测试结果表明,在频率43.5 GHz~45.5 GHz频段内,饱和功率输出大于5.7 W,增益大于10.5 dB,效率大于9.5%。

QuickLogic开放可重配置计算(QORC) 计划,以扩大嵌入式系统开发人员对开放FPGA技术的访问。QuickLogic与CHIPSAlliance成员Google和Antmicro合作开发的最初的开源开发工具,包括对QuickLogic的EOS S3低功耗语音和传感器处理MCU的完全支持,该MCU具有集成的嵌入式FPGA(eFPGA)及其PolarPro 3E FPGA系列。

QuickLogic公司和Antmicro推出了第一个完全开源的Arm CortexM4 MCU + eFPGA的SoC开发套件, QuickFeather?。Antmicro在Zephyr实时操作系统(RTOS)以及其开源Renode仿真框架中增加了对QuickFeather开发工具包的支持。这款小型开发板非常适合支持低功耗机器学习(ML)的IoT设备。

CHIPS联盟将继续专注于扩大其成员基础,这些组织来自不同行业的组织。QuickLogic是开源eFPGA IP和FPGA工具的领导者,将帮助我们推动FPGA领域的创新,并进一步消除消除开放式硬件设计障碍的使命。

(素材:chinaaet.如涉版权请联系删除)

共发射极放大器是三种基本单级放大器拓扑之一。BJT共发射极放大器一般用作反相电压放大器。晶体管的基极端为输入,集电极端为输出,而发射极为输入和输出共用(可连接至参考地端或电源轨),所谓“共射”即由此而来。

材料

ADALM2000主动学习模块

无焊面包板

五个电阻

一个50 kΩ可变电阻、电位计

一个小信号NPN晶体管(2N3904)

配置展现了用作共发射极放大器的NPN晶体管。选择适当的输出负载电阻RL,用于产生合适的标称集电极电流IC,VCE电压约为VP (5 V)的一半。通过可调电阻RPOT与RB来设置晶体管(IB)的标称偏置工作点,进而设置所需的IC。选择适当的分压器R1/R2,以便通过波形发生器W1提供足够大的输入激励衰减。考虑到在晶体管VBE的基极上会出现非常小的信号,这样做更容易查看发生器W1信号。衰减波形发生器W1信号通过4.7 uF电容交流耦合到晶体管基极,以免干扰直流偏置条件。

Q波段采用对脊鳍线微带过渡结构的5 W固态集成功率放大模块。利用HFSS软件对四路波导T型节以及对脊鳍线微带过渡结构分别进行模拟仿真,仿真结果表明,四路波导T型节插入损耗可以控制在0.1 dB以内,对脊鳍线微带过渡结构插入损耗可以控制在0.1 dB以内。对四路合成/分配器进行背对背安装,并进行直通测试,测试结果表明,在43.5 GHz~45.5 GHz频段内插入损耗在2 dB以内,可以推算合成效率大于80%。选用2 W的功放MMIC作为实验样片进行装配,采用金丝键的方式进行射频连接。对整个功率放大模块进行测试,测试结果表明,在频率43.5 GHz~45.5 GHz频段内,饱和功率输出大于5.7 W,增益大于10.5 dB,效率大于9.5%。

QuickLogic开放可重配置计算(QORC) 计划,以扩大嵌入式系统开发人员对开放FPGA技术的访问。QuickLogic与CHIPSAlliance成员Google和Antmicro合作开发的最初的开源开发工具,包括对QuickLogic的EOS S3低功耗语音和传感器处理MCU的完全支持,该MCU具有集成的嵌入式FPGA(eFPGA)及其PolarPro 3E FPGA系列。

QuickLogic公司和Antmicro推出了第一个完全开源的Arm CortexM4 MCU + eFPGA的SoC开发套件, QuickFeather?。Antmicro在Zephyr实时操作系统(RTOS)以及其开源Renode仿真框架中增加了对QuickFeather开发工具包的支持。这款小型开发板非常适合支持低功耗机器学习(ML)的IoT设备。

CHIPS联盟将继续专注于扩大其成员基础,这些组织来自不同行业的组织。QuickLogic是开源eFPGA IP和FPGA工具的领导者,将帮助我们推动FPGA领域的创新,并进一步消除消除开放式硬件设计障碍的使命。

(素材:chinaaet.如涉版权请联系删除)

上一篇:AIB技术的响应速度和带宽密度

上一篇:四路波导T型节功率合成分配器

热门点击

热门点击

- 串口设备间通过IO引脚产生电流倒灌

- NB-IoT发送传感器数据的应用

- 数字和模拟接口相连的传感器的数据

- 码灵半导体芯片所支持的操作系统

- 影响良率的裂纹和射频混频器

- 低功耗系统级功耗和芯片面积

- 电池监视器IC免受电过载的影响

- 共发射极放大器的NPN晶体管

- 耐能KL720芯片的3大优势

- 频段的5G路由器为数字用户线路

推荐技术资料

推荐技术资料

- 硬盘式MP3播放器终级改

- 一次偶然的机会我结识了NE0 2511,那是一个远方的... [详细]

公网安备44030402000607

公网安备44030402000607