Z86E2101ZDF 逻辑电路的功能及基本应用

发布时间:2020/2/10 12:22:08 访问次数:1218

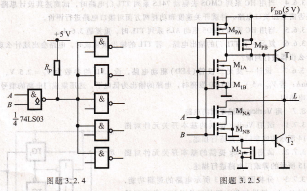

3.24 图题3,2.4所不为集电极开路门74LS03驱动5个CMOS逻辑门,已知0C门输出管截止时的漏电流v7=0.2 mA;负载门的参数为:ym(mml=4Ⅴ,ylLt mdx)=1v9JIL=rm=1uA。试计算上打电阻的值。

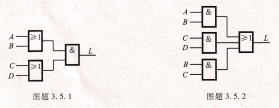

3.2.5 图题32,5表示一2输人端BiCMOs与非门电路,试分析该电路是怎样实现与非逻辑关系(即L=1・B)的。

路的抗实现门电路uL(max)=u1・630VoH(min)=0.980

3.4 砷化镓逻辑门电路

3.41 试计算3.4节介绍的两种砷干扰能力强。

3,5 逻辑描述中的几个问题

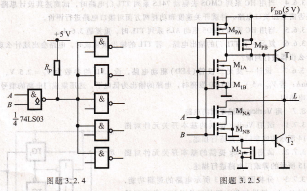

3.5,1 试对图题3.5,1所示电路的

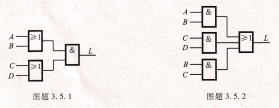

3.5,2 电路如图题3.5.2所示,试

图题3.5,1试计算它的噪声容限。

化镓逻辑门电路的噪声容限,并判断哪种电逻辑门进行变换,使其可以用单一的或非门用与非门实现。

图题3,5,2 数字系统中常用的各种数字部件,就其结构和工作原理而言可分为两大类,即组合逻辑电路和时序逻辑电路。本章首先介绍组合逻辑电路的定义、分析和设计,并阐述菀争冒险产生的原因及消除方法。然后讨论典型的中规模集成组合逻辑电路的功能及基本应用,它们包括编码器和译码器、数据选

择器和数据分配器、数值比较器、算术/逻辑运算单元等。最后介绍组合逻辑电路的Verilog HDL描述以及用可编程逻辑器件PLD的实现方法。

对于一个逻辑电路,其输出状态在任何时刻只取决于同一时刻的输入状态,而与电路原来的状态无关,这种电路被定义为组合逻辑电路。组合逻辑电路的一般框图如图4.0.1所示,其输出与输入之间的逻辑关系可用如下的逻辑函数来描述,即u=r(Al,A2,..,a3) (J=1,2,…,7n) (4.0.1)

式中找,A2,・・・,An一输入变量。

组合逻辑电路的结构具有,如下的特点:输出、输入之间没有反馈延迟通路;电路中不含具有记忆功能的元件。

图4,0.1 组合逻辑电路的一般框图,组合逻辑电路

3.24 图题3,2.4所不为集电极开路门74LS03驱动5个CMOS逻辑门,已知0C门输出管截止时的漏电流v7=0.2 mA;负载门的参数为:ym(mml=4Ⅴ,ylLt mdx)=1v9JIL=rm=1uA。试计算上打电阻的值。

3.2.5 图题32,5表示一2输人端BiCMOs与非门电路,试分析该电路是怎样实现与非逻辑关系(即L=1・B)的。

路的抗实现门电路uL(max)=u1・630VoH(min)=0.980

3.4 砷化镓逻辑门电路

3.41 试计算3.4节介绍的两种砷干扰能力强。

3,5 逻辑描述中的几个问题

3.5,1 试对图题3.5,1所示电路的

3.5,2 电路如图题3.5.2所示,试

图题3.5,1试计算它的噪声容限。

化镓逻辑门电路的噪声容限,并判断哪种电逻辑门进行变换,使其可以用单一的或非门用与非门实现。

图题3,5,2 数字系统中常用的各种数字部件,就其结构和工作原理而言可分为两大类,即组合逻辑电路和时序逻辑电路。本章首先介绍组合逻辑电路的定义、分析和设计,并阐述菀争冒险产生的原因及消除方法。然后讨论典型的中规模集成组合逻辑电路的功能及基本应用,它们包括编码器和译码器、数据选

择器和数据分配器、数值比较器、算术/逻辑运算单元等。最后介绍组合逻辑电路的Verilog HDL描述以及用可编程逻辑器件PLD的实现方法。

对于一个逻辑电路,其输出状态在任何时刻只取决于同一时刻的输入状态,而与电路原来的状态无关,这种电路被定义为组合逻辑电路。组合逻辑电路的一般框图如图4.0.1所示,其输出与输入之间的逻辑关系可用如下的逻辑函数来描述,即u=r(Al,A2,..,a3) (J=1,2,…,7n) (4.0.1)

式中找,A2,・・・,An一输入变量。

组合逻辑电路的结构具有,如下的特点:输出、输入之间没有反馈延迟通路;电路中不含具有记忆功能的元件。

图4,0.1 组合逻辑电路的一般框图,组合逻辑电路

公网安备44030402000607

公网安备44030402000607