SN54LS375AJ触发器电路的动态特性参数

发布时间:2020/1/17 12:36:22 访问次数:2422

为了改变这种阻塞的状况今Verilog提供了由“<=”符号构成的非阻塞型赋值语句。非阻塞型语句的执行过程是:首先计算语句块内部所有右边表达式的值,然后完成对左边寄存器变量的赋值操作,这些操作是并行执行的。例如,下面两条非阻塞型赋值语句的执行过程是;首先计算所有表达式右边的值并分别存储在暂存器中,即A的值被保存在一个暂存器中,而B+1的值被保存在另一个暂存器中,在begin和end之间所有非阻塞型赋值语句的右边表达式都被同时计算并存储后,对左边寄存器变量的赋值操作才会进行。这样,C的值等于B的原始值(而不是A的赋值)加1。

综上所述夕阻塞型赋值语句和非阻塞型赋值语句的主要区别是完成赋值操作的时间不同,前者的赋值操作是立即执行的,即执行后一句时,前一句的赋值已经完成;而后者的赋值操作要到顺序块内部的多条非阻塞型赋值语句运算结束时,才同时并行完成赋值操作,一旦赋值操作完成,语句块的执行也就结束了c.需要注意的是,在可综合的电路设计中9一个语句块的内部只允许出现唯一一种类型的赋值语句,而不允许阻塞型赋值语句和非阻塞型赋值语句二者同时出现。在时序电路的设计中)建议采用非阻塞型赋值语句。

锁存器和触发器的Veri|og建模实例,本节给出一些锁存器和触发器的行为级描述实例。例5.5.1是D锁存器,系Non~Blocking Assignment Statcmcnt的译称。

用yerFrog HDL描述锁存器和触发器,能端IE应输人的波形和相应0的波形,触发器的电路结构和工作原理.

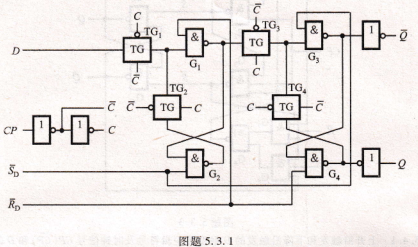

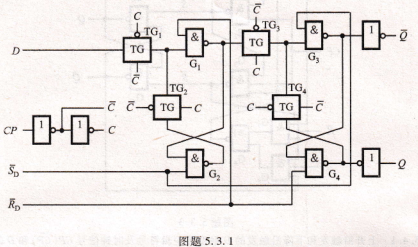

触发器的逻辑电路如图题5.3,1所示,确定其属于何种电路结构的触发器并分析工作原理。

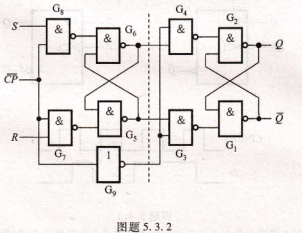

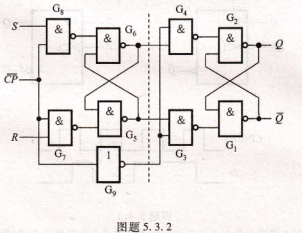

触发器的逻辑电路如图题5.3.2所示,确定其应属于何种电路结构的触发器。

图题5.3.2触发器的逻辑电路如图题5,3.3所示,确定其应属于何种电路结构的触,根据对图5.3.7的电路分析,列出其功能表。

图5.3.5的维持阻塞D触发器在D=1时保

图5,3,7中触发器电路的动态特性参数为,画出这种触发器的定时图。

触发器的逻辑功能,持时间tH为零,分析其原因。

tsu=5ns,JPHL=10 ns,PLI=G

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

为了改变这种阻塞的状况今Verilog提供了由“<=”符号构成的非阻塞型赋值语句。非阻塞型语句的执行过程是:首先计算语句块内部所有右边表达式的值,然后完成对左边寄存器变量的赋值操作,这些操作是并行执行的。例如,下面两条非阻塞型赋值语句的执行过程是;首先计算所有表达式右边的值并分别存储在暂存器中,即A的值被保存在一个暂存器中,而B+1的值被保存在另一个暂存器中,在begin和end之间所有非阻塞型赋值语句的右边表达式都被同时计算并存储后,对左边寄存器变量的赋值操作才会进行。这样,C的值等于B的原始值(而不是A的赋值)加1。

综上所述夕阻塞型赋值语句和非阻塞型赋值语句的主要区别是完成赋值操作的时间不同,前者的赋值操作是立即执行的,即执行后一句时,前一句的赋值已经完成;而后者的赋值操作要到顺序块内部的多条非阻塞型赋值语句运算结束时,才同时并行完成赋值操作,一旦赋值操作完成,语句块的执行也就结束了c.需要注意的是,在可综合的电路设计中9一个语句块的内部只允许出现唯一一种类型的赋值语句,而不允许阻塞型赋值语句和非阻塞型赋值语句二者同时出现。在时序电路的设计中)建议采用非阻塞型赋值语句。

锁存器和触发器的Veri|og建模实例,本节给出一些锁存器和触发器的行为级描述实例。例5.5.1是D锁存器,系Non~Blocking Assignment Statcmcnt的译称。

用yerFrog HDL描述锁存器和触发器,能端IE应输人的波形和相应0的波形,触发器的电路结构和工作原理.

触发器的逻辑电路如图题5.3,1所示,确定其属于何种电路结构的触发器并分析工作原理。

触发器的逻辑电路如图题5.3.2所示,确定其应属于何种电路结构的触发器。

图题5.3.2触发器的逻辑电路如图题5,3.3所示,确定其应属于何种电路结构的触,根据对图5.3.7的电路分析,列出其功能表。

图5.3.5的维持阻塞D触发器在D=1时保

图5,3,7中触发器电路的动态特性参数为,画出这种触发器的定时图。

触发器的逻辑功能,持时间tH为零,分析其原因。

tsu=5ns,JPHL=10 ns,PLI=G

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607