NJM2538V(TE1)LUT确定的逻辑功能

发布时间:2020/1/16 13:30:32 访问次数:816

NJM2538V(TE1)并自动对逻辑电路进行划分、布局和布线,然后按照一定的格式生成编程数据文件,再通过编程电缆将编程数据写人CPLD中。有关可编程器件的开发过程可以参阅附录C。

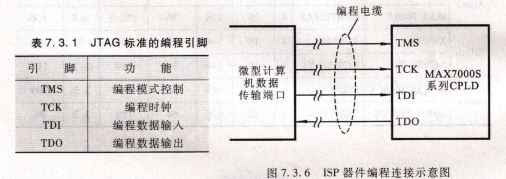

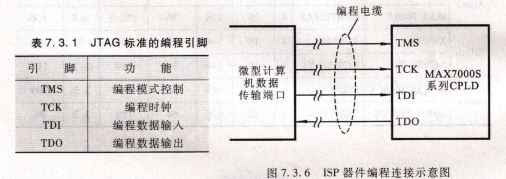

目前,绝大部分CPLD器件具有ISP功能。例如,Akn公司的MAX7000S(5V)、 MAX7000A(3..3Ⅴ)和MAX7000B(2.5Ⅴ)系列, Xilinx公司的XC9500系列以及Lathce公司的CPLD器件等。ISP器件的编程必须具各三个条件:ISP专用编程电缆、微机、ISP编程软件。编程时,用户首先将ISP编程电缆的一端接到微机的数据传输端口上①,另一端接到电路板上被编程器件的ISP接口上,然后通过编程软件发出编程命令,将编程数据传送到芯片中。

ISP接口也不完全相同,但基本上都支持中都设有JTAG规定的4个I/0引脚。各引脚6所示是MAX7000S系列CPLD器件编程连接程电缆微杠传,ISP器件编程连接示意图

TDO的数据可以用于编程校验,也可以作为多个CPLD串行编程时下一个CPLD器件的输入数据,如图7,3,1所示。多数CPLD的这4个编程引脚也可以作为用户I/0使用。

与后面将要介绍的FPGA相比,尽管CPLD在电路规模和灵活性方面不如FPGA,但是它的可加密性和传输延时预知性,使得CPLD仍广泛应用于数字系统设计中。

目前,各大生产厂商仍不断开发出集成度更高、速度更快(功耗更低的CPLD新产品,核心工作电源可以低到1.8V。表7.4.1所示为几种典型的CPLD产品。

可以是并口、串口或USB口,视编程软件所支持的端口而定。

系Joint Test Action Group的缩写,指由该组织制定的IEEE 1149,l接口标准。

复杂可编程逻辑器件,而是采用查我表(LUT①)实现逻辑函数。这种不同于CPLD结构的特点,使FPGA中可以包含数量众多的LUT和触发器,从而能够实现更大规模、更复杂的逻辑电路,避免了“与-或”阵列结构上的限制和触发器及yo端数量上的限制。

近年来,生产工艺上的进步大大降低了FPGA的成本,其功能及性能上的优越性更为突出。因此,FPGA已成为目前设计数字电路或系统的首选器件之一。

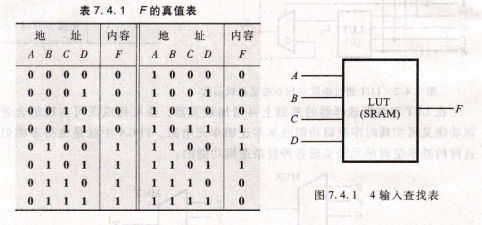

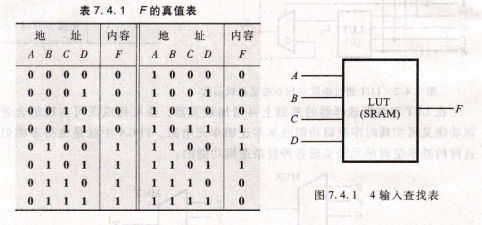

FPGA中编程实现逻辑功能的基本原理,在FPGA多使用4个输入、1个输出的以每一个的本目的值写人对应的内容输出,在F端便得到该组输人信号逻辑运算厂的真值表,而触发器FPGA中的,找出地址,当用户通过原理图或HDL语言描述了一个逻辑电路件会自动计算逻辑电路的所有可能的结果(真值表),并把以后,FPGA开发软结果写入SRAM,这一过程就是所谓的编程。此后,SRAM中的内容始终保持不变,LUT就具有了确定的逻辑功能。由于SRAM具有数据易失性,即一旦断电,其原有的逻辑功能将消失。所以FPGA一般需要一个外部的PROM保存编程数据。上电后,FPGA首先从PROM中读人编程数据进行初始化,然后才开始正常工作。

系1 ook-Up Tablc的缩写。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

NJM2538V(TE1)并自动对逻辑电路进行划分、布局和布线,然后按照一定的格式生成编程数据文件,再通过编程电缆将编程数据写人CPLD中。有关可编程器件的开发过程可以参阅附录C。

目前,绝大部分CPLD器件具有ISP功能。例如,Akn公司的MAX7000S(5V)、 MAX7000A(3..3Ⅴ)和MAX7000B(2.5Ⅴ)系列, Xilinx公司的XC9500系列以及Lathce公司的CPLD器件等。ISP器件的编程必须具各三个条件:ISP专用编程电缆、微机、ISP编程软件。编程时,用户首先将ISP编程电缆的一端接到微机的数据传输端口上①,另一端接到电路板上被编程器件的ISP接口上,然后通过编程软件发出编程命令,将编程数据传送到芯片中。

ISP接口也不完全相同,但基本上都支持中都设有JTAG规定的4个I/0引脚。各引脚6所示是MAX7000S系列CPLD器件编程连接程电缆微杠传,ISP器件编程连接示意图

TDO的数据可以用于编程校验,也可以作为多个CPLD串行编程时下一个CPLD器件的输入数据,如图7,3,1所示。多数CPLD的这4个编程引脚也可以作为用户I/0使用。

与后面将要介绍的FPGA相比,尽管CPLD在电路规模和灵活性方面不如FPGA,但是它的可加密性和传输延时预知性,使得CPLD仍广泛应用于数字系统设计中。

目前,各大生产厂商仍不断开发出集成度更高、速度更快(功耗更低的CPLD新产品,核心工作电源可以低到1.8V。表7.4.1所示为几种典型的CPLD产品。

可以是并口、串口或USB口,视编程软件所支持的端口而定。

系Joint Test Action Group的缩写,指由该组织制定的IEEE 1149,l接口标准。

复杂可编程逻辑器件,而是采用查我表(LUT①)实现逻辑函数。这种不同于CPLD结构的特点,使FPGA中可以包含数量众多的LUT和触发器,从而能够实现更大规模、更复杂的逻辑电路,避免了“与-或”阵列结构上的限制和触发器及yo端数量上的限制。

近年来,生产工艺上的进步大大降低了FPGA的成本,其功能及性能上的优越性更为突出。因此,FPGA已成为目前设计数字电路或系统的首选器件之一。

FPGA中编程实现逻辑功能的基本原理,在FPGA多使用4个输入、1个输出的以每一个的本目的值写人对应的内容输出,在F端便得到该组输人信号逻辑运算厂的真值表,而触发器FPGA中的,找出地址,当用户通过原理图或HDL语言描述了一个逻辑电路件会自动计算逻辑电路的所有可能的结果(真值表),并把以后,FPGA开发软结果写入SRAM,这一过程就是所谓的编程。此后,SRAM中的内容始终保持不变,LUT就具有了确定的逻辑功能。由于SRAM具有数据易失性,即一旦断电,其原有的逻辑功能将消失。所以FPGA一般需要一个外部的PROM保存编程数据。上电后,FPGA首先从PROM中读人编程数据进行初始化,然后才开始正常工作。

系1 ook-Up Tablc的缩写。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607