5023821272 内部数据进行交换的接口电路

发布时间:2020/1/16 17:43:37 访问次数:687

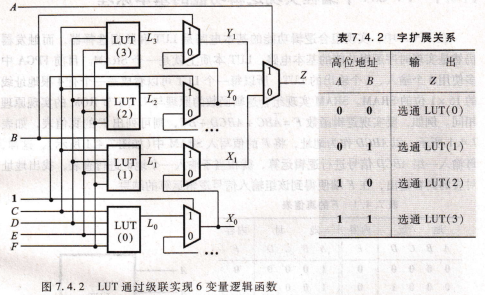

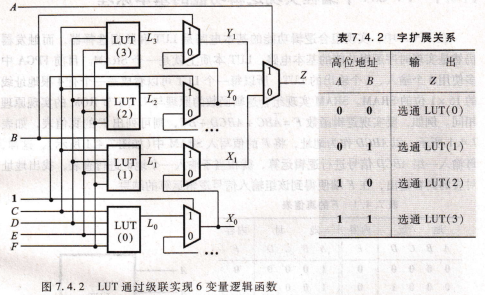

5023821272由于一般的LUT为4输入结构,所以,当要实现多于4变量的逻辑函数时,就需要用多个LUT级联来实现。一般FPGA中的LUT是通过数据选择器完成级联的。图7.4.2所示是由4个LUT和若干个2选1数据选择器实现6变量任意逻辑函数的原理图。该电路实际上将4个16×1位的LUT扩展成为64×1位。A、B相当于6位地址的最高2位,它们取不同值时,输出与LUT的关系如表7.4.2所示。

变量逻辑函数,在LUT上再增加触发器,辑功能又可实现时序逻辑功能的基本,逻辑单元电路,这样的基本逻辑单元来实现各种复杂逻辑功能的。

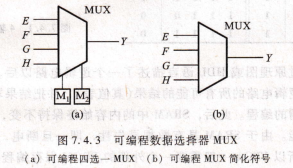

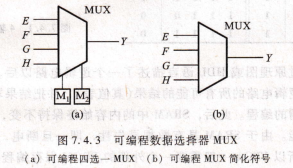

可编程数据选择器MUⅩ,(a〉可编程四选一MUX (b)可编程MUX简化符号.

可编程数据选择器MUX在FPGA中也充当着重要角色。例如,在图7,4,3(a)中,编程时在SRAM存储单元M1、M2中写入0或1,就可以确定被选中的输人通道与输出相连。此时MUX就是可编程的数据开关,编程后,开存储器、复杂可编程器件和明场可编程闸阵列.

字扩展关系部引脚数据与内部数据进行交换的接口电路,通过编程可将I/0引脚设置成输入、输出和双向等不同的功能。IOB分布在芯片的四周。

延时锁环DLL可以控制和修正内部各部分时钟的传输延迟时间,保证逻辑电路可靠地工作。同时,也可以产生相位滞后0°、90°、180°和270°的时钟脉冲,还可产生倍频或分频时钟,分频系数可以是1.5、2、2.5、3、4、5、8、16等。CLB之间的空隙部分是布线区①,分布着可编程布线资源。通过它们实现CLB与CLB之间、CLB与IOB之间以及全局时钟等信号与CLB和IOB之间的连接。

在Xilinx公司的高性能产品中,已将乘法器、数字信号处理器等集成在FPGA中,大大增强了FPGA的功能。同时,为了使芯片稳定可靠地工作,其内部都设有数字时钟管理模块。由于这些内容已超出本书讨论范围,所以此处只介绍FPGA中几个最基本的功能模块。

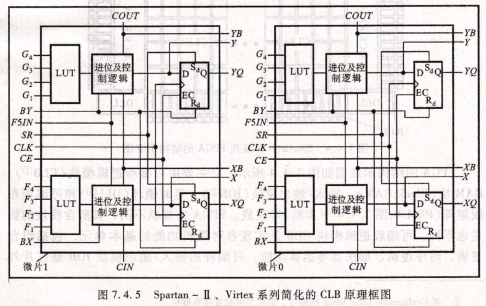

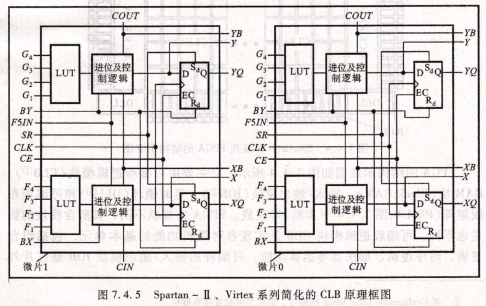

可编程逻辑模块CLB,CLB是FPGA中的基本逻辑模块,它可实现绝大多数的逻辑功能,其简化的原理框图如图7.4.5所示。构成CLB的基础是逻辑单元(LC②),一个LC中包括一个4输人LUT、进位及控制逻辑和一个D触发器(EC为时钟使能控制端)。每个CLB包含4个LC,并将每2个LC组织在1个微片(slice)中,图中

可见有2个微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4个微片,即含有8个LC。CLB的输入来自可编程布线区,其输出再回送到内部布线区。

Spartan-Ⅱ、Ⅴirtex系列简化的CLB原理框图

实际上,PGA采用多层布局布线结构,并非只能在模块间的空隙处布线。

Logic Cell的缩写,存储器、复杂可编程器件和明场可编程门阵列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

5023821272由于一般的LUT为4输入结构,所以,当要实现多于4变量的逻辑函数时,就需要用多个LUT级联来实现。一般FPGA中的LUT是通过数据选择器完成级联的。图7.4.2所示是由4个LUT和若干个2选1数据选择器实现6变量任意逻辑函数的原理图。该电路实际上将4个16×1位的LUT扩展成为64×1位。A、B相当于6位地址的最高2位,它们取不同值时,输出与LUT的关系如表7.4.2所示。

变量逻辑函数,在LUT上再增加触发器,辑功能又可实现时序逻辑功能的基本,逻辑单元电路,这样的基本逻辑单元来实现各种复杂逻辑功能的。

可编程数据选择器MUⅩ,(a〉可编程四选一MUX (b)可编程MUX简化符号.

可编程数据选择器MUX在FPGA中也充当着重要角色。例如,在图7,4,3(a)中,编程时在SRAM存储单元M1、M2中写入0或1,就可以确定被选中的输人通道与输出相连。此时MUX就是可编程的数据开关,编程后,开存储器、复杂可编程器件和明场可编程闸阵列.

字扩展关系部引脚数据与内部数据进行交换的接口电路,通过编程可将I/0引脚设置成输入、输出和双向等不同的功能。IOB分布在芯片的四周。

延时锁环DLL可以控制和修正内部各部分时钟的传输延迟时间,保证逻辑电路可靠地工作。同时,也可以产生相位滞后0°、90°、180°和270°的时钟脉冲,还可产生倍频或分频时钟,分频系数可以是1.5、2、2.5、3、4、5、8、16等。CLB之间的空隙部分是布线区①,分布着可编程布线资源。通过它们实现CLB与CLB之间、CLB与IOB之间以及全局时钟等信号与CLB和IOB之间的连接。

在Xilinx公司的高性能产品中,已将乘法器、数字信号处理器等集成在FPGA中,大大增强了FPGA的功能。同时,为了使芯片稳定可靠地工作,其内部都设有数字时钟管理模块。由于这些内容已超出本书讨论范围,所以此处只介绍FPGA中几个最基本的功能模块。

可编程逻辑模块CLB,CLB是FPGA中的基本逻辑模块,它可实现绝大多数的逻辑功能,其简化的原理框图如图7.4.5所示。构成CLB的基础是逻辑单元(LC②),一个LC中包括一个4输人LUT、进位及控制逻辑和一个D触发器(EC为时钟使能控制端)。每个CLB包含4个LC,并将每2个LC组织在1个微片(slice)中,图中

可见有2个微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4个微片,即含有8个LC。CLB的输入来自可编程布线区,其输出再回送到内部布线区。

Spartan-Ⅱ、Ⅴirtex系列简化的CLB原理框图

实际上,PGA采用多层布局布线结构,并非只能在模块间的空隙处布线。

Logic Cell的缩写,存储器、复杂可编程器件和明场可编程门阵列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607