SM2253EK��Ÿ��ŵ����Ʒ���

����ʱ��:2019/11/4 22:52:10 ���ʴ���:1001

SM2253EK���ֵ�Ÿ��ŵ����Ʒ���,ǰ�������������Ƹ��ŵĸ��ּ�����ʩ,���ڽ�����������Щ������ʩ�Գ�����Ÿ��ŵ����Ʒ�����

��Դ���ŵ����Ʒ���,��Դ��ѹ�ϳ������и��ŵ�ѹ,��Դ���Ŷ���Խ���ͬһ�����ϵ��õ��豸�͵���������,���������Դ���ŵIJ���ԭ��

��ͨ���Ը���(��е���㡢�̵����Ϳ��ص�)��˲̬���ɹ��̿ɲ��������ѹ��

���ڵ�Դ��ѹ�ϡ�

�������ϵͳ�Ļ����丽���ĸ�Ƶ�豸������������Դ֮���е�·�ԡ���������������Ϻͷ������,����Ƶ�������ѹ�������ϵͳ��

����ЧӦ����·��ͨ�ϼ����ֹ��ϵ������ϵͳ�����쳣��ѹ,�Ӷ��γɵ�Դ���š�

���ڵ����߱���������ЧӦ,�ɽ�����Ӧ�����ĸ��ŵ�ѹ���ӵ�Դ��ѹ�ϡ�

�ڸ�ѹ������Ͽ����е��ηŵ�,�ڵ�ѹ�Ե͵ĸ�ѹ���������ʱҲ������Ե�������ķŵ�����,���ֵ����ߵķŵ�����Ҳ�����ɵ�Դ���š�

���Ƶ�Դ���ſɲ�����ѹ�����Ρ����롢�˲��������������������ӵصȼ�����ʩ��

��Դ��ѹ,ͨ����ѹ��·�����������������,��ʹ��Դ���ŵõ�˥����������Դ��ѹ������������������Ͻϳ�ʱ��仯�IJ��ȶ���ѹ,һ�����ѹ�豸��ʹ�仯��10%~20%�IJ��ȶ������ѹ,�ȶ���1%~5%,����Ӧʱ��Ϊ��Դ�仯��һ������,�����ѹ�豸�����ȶ�̫��ĵ�ѹ�����������ѹ������Ƶ�ʸ��ڵ�ԴƵ��10������,��ѹ�������ϵ���ģ���Ų�����ϵ��μ���,������ٵĵ�ѹ����������ɸ��š�

����������Ҳ��Ϊ��ӿ������,�������Ƶ����ڵ�Դ��ѹ�ϵļ�����岨��,����Ӧʱ���൱��,��С��100 ns����ӿ����������Ҫ�ص��������һ��ѹ�Ĺ�ϵ�������������,���������Ӻͼ���,����ֵҲ�����仯,����ӿ������Ҳ����Ϊ����������ӿ�����������Կ�����ʽ��ʾ:

r=(��/c)a (10-14)

ʽ��,rΪ������ӿ�������ĵ���,��Ϊ������ӿ�������ϵĵ�ѹ,C�dz���,���Ƿ�����ϵ����������ϵ����Խ��,˵��������Խ�á�

��ʾ��ӿ������������ӿ��ѹ�����IJ�������ӿ��ѹ����ֵ����ӿ��������ֵ�������յ���ӿ��������ֵ��������ʹ�õIJ��ϲ�ͬ,��ӿ�������м���Ʒ��,����SiC��ӿ����

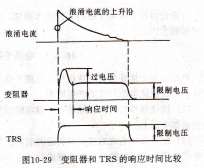

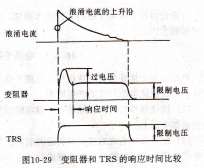

��;��ѹ�����������մɽṹ��ӿ������;���ɶ�����Ҳ����Ϊ��ӿ������;����п������(���ѹ������)������ѹ��ƽǯλԪ��TRS�ȡ�TRS�����ð뵼��ѩ��ЧӦ��һ�ֶ�����,����Ӧʱ��ԼΪ5ns����,©����Ҳֻ��5uA��ͼ10-29�Ƕ�����ͬ�ĵ������ȵ���ӿ����,������(һ�����ӿ������)����Ӧʱ�䳤,��TRS����Ӧʱ��̡ܶ�

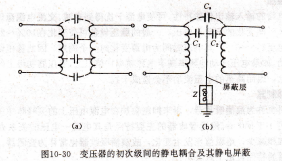

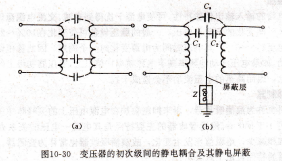

��Դ��ѹ���ĵ�����,���ڵ�Դ��ѹ���ij��μ���Ȧ���ú���,��������֮��������pF���ҵķֲ�,����,��ͼ10-30(a)��ʾ�����ֲַ���������������,����Ƶ������Ҳ�ܺ�,�Ը�Ƶ�����кܵ͵��迹������ѵ����еĸ�Ƶ�����������ͨ�����ֵ�����ϵ���ѹ���Ĵμ���Ȧ�ϡ����þ������εķ��������������ֵ�Ÿ���,ͼ10-30(b)�л������ڱ�ѹ����������ʹμ�����֮������������ε�ʾ��ͼ���������������ѹ���ij��������,�ڴ���������0.02~0:03.��������TRS����Ӧʱ��Ƚ�mm��ı�ͭƤ��һ��,ͭƤ��ʼ����ĩ�˱�����3~5mm���ص�����,���ص�����Ҫ���Ե�������������β����ټ�һ��,�������β�֮��ҲҪ��Ե,��Ч�����á������迹z�����εĹؼ�֮һ,���β��������Ҫ�����ܵض̺ʹ֡�����,���β�������������β�ĽӴ�����Ҫ���ú�С,����Ҫ�ܳ����ȶ�������Ҳ��ֱ���������β��ͭƤ������,ʹ���������β�Ϊһ��,�����㲻���ڽӴ��ɿ��������⡣��������ͭƤ�ĵ��Ҫ��һ�㵼��С,���Եõ���С�������迹��

��ѹ���ij��μ���ľ�����ϼ��侲������,ͼ10-30(b)��ʾ��Cs�Ǽ������β�֮��,���μ�������Ȼ�д�ķֲ�����,�����������β㲻����ȫ��յذ�ס��������,��Ȼ��һ���ֵ������ƹ����β㵽��μ�,����д�ķֲ����ݡ��ݲ���,һ��200VA���ҵ�С�͵�Դ��ѹ��,�������μ������β������ԼΪ500pF,�����˵,�����β㲻�ӵصĻ�,���μ���ķֲ�����Ϊ250 pF���ҡ���

���β�ӵغ�,���μ��ֲ����ݽ�Ϊ20 pF����,����Dzд�ķֲ�����Cs��ֵ�������跨��С���ֲд�ֲ�����,����,������ʱ�صؽ�����Ŀ�����խһЩ,�������β���Ⱦ����ܿ�һЩ,ʹй©�ĵ����߱�ø��١���������,����ʹ��ѹ���ľ��������������������Ĵ�ʩ,��һһ�о��ˡ�

��Դ��ȥ���˲�,����ϵͳ��������ĵ�ѹԴ,����ͨ����Դ�����迹�γɸ��õ��·֮�����ϡ���������������ӿ,��������ѹӦʱ�������Ƶ�ѹ.

�첽ʱ���·�ķ�����ͬ��ʱ���·�ķ�����Ҫ����Щ��֮ͬ��?

�����첽ʱ���·ʱ,Ϊʲô��Ҫ�г�ÿ��������ʱ���źŵ�������ʽ?

Ϊʲô�ڷ����첽ʱ���·��״̬ת��ʱ,���밴�ź����õ�˳���ÿ������

����������Ƶ�,����ȷ����·�Ĵ�̬?

�첽ʱ���·��ÿ��״̬ת��ʱΪʲô����ֶ�ʱ��IJ��ȶ�״̬?���ֲ���

��ʱ��ij������ŵ�·�ʹ��������ӳ�ʱ����ʲô��ϵ?�����������Щ��

�����?

Ϊʲô�첽ʱ���·�������źű����ڵ�·ת��״̬�ȶ�֮������������ı�?

���ڽ���������ϵͳ�й㷺Ӧ�õļ��ֵ���ʱ�������ܵ�·�D�Ĵ�������λ�Ĵ����ͼ�����,�����������ϵ�·һ��,���Թ��������ܼ������ӵ�����ϵͳ���Ĵ�������λ�Ĵ����ͼ������кܶ�������й�ģ���ɵ�·���Ͳ�Ʒ,����ֱ��Ӧ����һЩ�ϼ�����ϵͳ�������ڽϸ��ӵ�ʱ������·,Ŀǰһ��Ӧѡ��ɱ����������ר�ü��ɵ�·ʵ��,����������С��ģ���ɵ�·��װ�����������ܵ�һЩ�й�ģ���ɵ�·���Ͳ�Ʒһ�㶼���н����ƵĹ���,��һЩ�ɱ���������ļ��ɿ����������ѽ�������Ϊ����ģ�顱�ṩ���û�ʹ��,�Ӷ�ʹ����ϵͳ����Ƶõ������,����˽���Щ�������ɵ�·�Ĺ���ԭ���͵�·�ṹ,��������EDA������Ƹ��������ܵ�����ϵͳҲ������ġ�

�Ĵ�������λ�Ĵ���,�Ĵ���������ϵͳ�������洢���������ݵ���������1���������ɴ洢1λ����������,�洢��λ���������ݵļĴ�����Ҫ�ü�����������ɡ���8�����������ɵ�8λCMOS�Ĵ���74HC/HCT374����ͼ,��ͼ

6.5.1��ʾ���������й�ģ���ɵ�·һ��,��·�����е����˶ˡ�����˶���

���˻����·,�����ִ����ɵ�·���ص�֮һ����һ����ʹоƬ�ڲ�����·

���ⲿ��·�õ���Ч����,ʹ�ڲ������ֵĹ��������ȶ��ɿ�;��һ����,���������ˡ�������Կ��Լذ���ϵ�б�����������,�Ӷ�����˵�·.

SM2253EK���ֵ�Ÿ��ŵ����Ʒ���,ǰ�������������Ƹ��ŵĸ��ּ�����ʩ,���ڽ�����������Щ������ʩ�Գ�����Ÿ��ŵ����Ʒ�����

��Դ���ŵ����Ʒ���,��Դ��ѹ�ϳ������и��ŵ�ѹ,��Դ���Ŷ���Խ���ͬһ�����ϵ��õ��豸�͵���������,���������Դ���ŵIJ���ԭ��

��ͨ���Ը���(��е���㡢�̵����Ϳ��ص�)��˲̬���ɹ��̿ɲ��������ѹ��

���ڵ�Դ��ѹ�ϡ�

�������ϵͳ�Ļ����丽���ĸ�Ƶ�豸������������Դ֮���е�·�ԡ���������������Ϻͷ������,����Ƶ�������ѹ�������ϵͳ��

����ЧӦ����·��ͨ�ϼ����ֹ��ϵ������ϵͳ�����쳣��ѹ,�Ӷ��γɵ�Դ���š�

���ڵ����߱���������ЧӦ,�ɽ�����Ӧ�����ĸ��ŵ�ѹ���ӵ�Դ��ѹ�ϡ�

�ڸ�ѹ������Ͽ����е��ηŵ�,�ڵ�ѹ�Ե͵ĸ�ѹ���������ʱҲ������Ե�������ķŵ�����,���ֵ����ߵķŵ�����Ҳ�����ɵ�Դ���š�

���Ƶ�Դ���ſɲ�����ѹ�����Ρ����롢�˲��������������������ӵصȼ�����ʩ��

��Դ��ѹ,ͨ����ѹ��·�����������������,��ʹ��Դ���ŵõ�˥����������Դ��ѹ������������������Ͻϳ�ʱ��仯�IJ��ȶ���ѹ,һ�����ѹ�豸��ʹ�仯��10%~20%�IJ��ȶ������ѹ,�ȶ���1%~5%,����Ӧʱ��Ϊ��Դ�仯��һ������,�����ѹ�豸�����ȶ�̫��ĵ�ѹ�����������ѹ������Ƶ�ʸ��ڵ�ԴƵ��10������,��ѹ�������ϵ���ģ���Ų�����ϵ��μ���,������ٵĵ�ѹ����������ɸ��š�

����������Ҳ��Ϊ��ӿ������,�������Ƶ����ڵ�Դ��ѹ�ϵļ�����岨��,����Ӧʱ���൱��,��С��100 ns����ӿ����������Ҫ�ص��������һ��ѹ�Ĺ�ϵ�������������,���������Ӻͼ���,����ֵҲ�����仯,����ӿ������Ҳ����Ϊ����������ӿ�����������Կ�����ʽ��ʾ:

r=(��/c)a (10-14)

ʽ��,rΪ������ӿ�������ĵ���,��Ϊ������ӿ�������ϵĵ�ѹ,C�dz���,���Ƿ�����ϵ����������ϵ����Խ��,˵��������Խ�á�

��ʾ��ӿ������������ӿ��ѹ�����IJ�������ӿ��ѹ����ֵ����ӿ��������ֵ�������յ���ӿ��������ֵ��������ʹ�õIJ��ϲ�ͬ,��ӿ�������м���Ʒ��,����SiC��ӿ����

��;��ѹ�����������մɽṹ��ӿ������;���ɶ�����Ҳ����Ϊ��ӿ������;����п������(���ѹ������)������ѹ��ƽǯλԪ��TRS�ȡ�TRS�����ð뵼��ѩ��ЧӦ��һ�ֶ�����,����Ӧʱ��ԼΪ5ns����,©����Ҳֻ��5uA��ͼ10-29�Ƕ�����ͬ�ĵ������ȵ���ӿ����,������(һ�����ӿ������)����Ӧʱ�䳤,��TRS����Ӧʱ��̡ܶ�

��Դ��ѹ���ĵ�����,���ڵ�Դ��ѹ���ij��μ���Ȧ���ú���,��������֮��������pF���ҵķֲ�,����,��ͼ10-30(a)��ʾ�����ֲַ���������������,����Ƶ������Ҳ�ܺ�,�Ը�Ƶ�����кܵ͵��迹������ѵ����еĸ�Ƶ�����������ͨ�����ֵ�����ϵ���ѹ���Ĵμ���Ȧ�ϡ����þ������εķ��������������ֵ�Ÿ���,ͼ10-30(b)�л������ڱ�ѹ����������ʹμ�����֮������������ε�ʾ��ͼ���������������ѹ���ij��������,�ڴ���������0.02~0:03.��������TRS����Ӧʱ��Ƚ�mm��ı�ͭƤ��һ��,ͭƤ��ʼ����ĩ�˱�����3~5mm���ص�����,���ص�����Ҫ���Ե�������������β����ټ�һ��,�������β�֮��ҲҪ��Ե,��Ч�����á������迹z�����εĹؼ�֮һ,���β��������Ҫ�����ܵض̺ʹ֡�����,���β�������������β�ĽӴ�����Ҫ���ú�С,����Ҫ�ܳ����ȶ�������Ҳ��ֱ���������β��ͭƤ������,ʹ���������β�Ϊһ��,�����㲻���ڽӴ��ɿ��������⡣��������ͭƤ�ĵ��Ҫ��һ�㵼��С,���Եõ���С�������迹��

��ѹ���ij��μ���ľ�����ϼ��侲������,ͼ10-30(b)��ʾ��Cs�Ǽ������β�֮��,���μ�������Ȼ�д�ķֲ�����,�����������β㲻����ȫ��յذ�ס��������,��Ȼ��һ���ֵ������ƹ����β㵽��μ�,����д�ķֲ����ݡ��ݲ���,һ��200VA���ҵ�С�͵�Դ��ѹ��,�������μ������β������ԼΪ500pF,�����˵,�����β㲻�ӵصĻ�,���μ���ķֲ�����Ϊ250 pF���ҡ���

���β�ӵغ�,���μ��ֲ����ݽ�Ϊ20 pF����,����Dzд�ķֲ�����Cs��ֵ�������跨��С���ֲд�ֲ�����,����,������ʱ�صؽ�����Ŀ�����խһЩ,�������β���Ⱦ����ܿ�һЩ,ʹй©�ĵ����߱�ø��١���������,����ʹ��ѹ���ľ��������������������Ĵ�ʩ,��һһ�о��ˡ�

��Դ��ȥ���˲�,����ϵͳ��������ĵ�ѹԴ,����ͨ����Դ�����迹�γɸ��õ��·֮�����ϡ���������������ӿ,��������ѹӦʱ�������Ƶ�ѹ.

�첽ʱ���·�ķ�����ͬ��ʱ���·�ķ�����Ҫ����Щ��֮ͬ��?

�����첽ʱ���·ʱ,Ϊʲô��Ҫ�г�ÿ��������ʱ���źŵ�������ʽ?

Ϊʲô�ڷ����첽ʱ���·��״̬ת��ʱ,���밴�ź����õ�˳���ÿ������

����������Ƶ�,����ȷ����·�Ĵ�̬?

�첽ʱ���·��ÿ��״̬ת��ʱΪʲô����ֶ�ʱ��IJ��ȶ�״̬?���ֲ���

��ʱ��ij������ŵ�·�ʹ��������ӳ�ʱ����ʲô��ϵ?�����������Щ��

�����?

Ϊʲô�첽ʱ���·�������źű����ڵ�·ת��״̬�ȶ�֮������������ı�?

���ڽ���������ϵͳ�й㷺Ӧ�õļ��ֵ���ʱ�������ܵ�·�D�Ĵ�������λ�Ĵ����ͼ�����,�����������ϵ�·һ��,���Թ��������ܼ������ӵ�����ϵͳ���Ĵ�������λ�Ĵ����ͼ������кܶ�������й�ģ���ɵ�·���Ͳ�Ʒ,����ֱ��Ӧ����һЩ�ϼ�����ϵͳ�������ڽϸ��ӵ�ʱ������·,Ŀǰһ��Ӧѡ��ɱ����������ר�ü��ɵ�·ʵ��,����������С��ģ���ɵ�·��װ�����������ܵ�һЩ�й�ģ���ɵ�·���Ͳ�Ʒһ�㶼���н����ƵĹ���,��һЩ�ɱ���������ļ��ɿ����������ѽ�������Ϊ����ģ�顱�ṩ���û�ʹ��,�Ӷ�ʹ����ϵͳ����Ƶõ������,����˽���Щ�������ɵ�·�Ĺ���ԭ���͵�·�ṹ,��������EDA������Ƹ��������ܵ�����ϵͳҲ������ġ�

�Ĵ�������λ�Ĵ���,�Ĵ���������ϵͳ�������洢���������ݵ���������1���������ɴ洢1λ����������,�洢��λ���������ݵļĴ�����Ҫ�ü�����������ɡ���8�����������ɵ�8λCMOS�Ĵ���74HC/HCT374����ͼ,��ͼ

6.5.1��ʾ���������й�ģ���ɵ�·һ��,��·�����е����˶ˡ�����˶���

���˻����·,�����ִ����ɵ�·���ص�֮һ����һ����ʹоƬ�ڲ�����·

���ⲿ��·�õ���Ч����,ʹ�ڲ������ֵĹ��������ȶ��ɿ�;��һ����,���������ˡ�������Կ��Լذ���ϵ�б�����������,�Ӷ�����˵�·.

�������

�������

- FQP34N20�¶���ʱ���·

- SG2813J/883B 6��-64��������

- SN74HC393NS 16λȫ��ǰ��λ����

- HA13627����˵�����

- RD120009N˲̬����������̬������

- SMD2920P300TF����������������

- ZM4749A-GS08����ķ�����BJT��

- MAX1232C/EPA ģ��

- XC1701LPCʱ����

- STD302S�������伫�Ŵ��·

�Ƽ���������

�Ƽ���������

- ��ѩ��������

- ������һ��dz���Ȥ��ͬʱ����һ�������Ѷȵ��淨��EDE2116AB... [��ϸ]

��������44030402000607

��������44030402000607