HDSP-431G设计项目的编译

发布时间:2019/10/25 22:00:34 访问次数:625

HDSP-431G上述工作完成后,由软件自动完成布局与布线工作,它以最优的方式对逻G件布局,并准确地完成元件之间的连线。

时序仿真使用包含延时信息的编译网表,不仅测试逻辑功能,还测试设计的逻辑在目标器件中最差情况下的时序关系,它和器件的实际工作情况基本一致,因此对整个设计项目进行时序仿真,分析其时序关系,评估设计的性能是非常必要的。

器件的编程与测试,在对设计的文件进行处理时,软件会自动产生供编程用的数据文件。对CPLD器件,编程文件为熔丝图文件;而对FPGA器件,编程文件为位流数据文件。对具有在系统编程功能的器件,可以使用相应的编程软件,通过编程电缆直接将编程数据写入到器件中。对没有在系统编程接口的器件,则需要使用专用编程器,才能对器件编程。对器件的编程完成后,需要对器件的功能进行

实际测试。

对于熟悉MAX+PLUS Ⅱ的用户,在启动Quartus Ⅱ软件后,选择Tods|Customize…菜单命令,在对话框的Genera1页面选择MAX+PLUS Ⅱ选项,单击Apply按钮后,重新启动Quartus Ⅱ软件,则此时主窗口图形用户界面与

MAX+PLUS Ⅱ软件的界面类似。

下面以Ⅴerilog HDL设计十进制计数器为例,从输入设计文件、设计项目的编译、设计项目的仿真验证和器件编程四个方面对Quartus Ⅱ软件的使用进行简单介绍。受篇幅所限,原理图(或称为方块图)输人方式不作介绍,详细使用方法可以参考软件帮助文档。

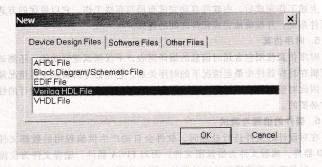

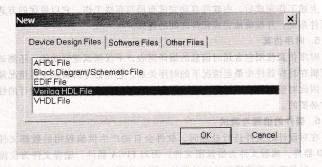

使用向导建立新工程,并输入设计文件,启动Quartus Ⅱ软件后,从Fne菜单下选择New Project Wizzard,按照提示输人设计项目的路径,项目名称以及顶层模块的名称。然后选择Fne|New...命令,出现图B.2.1所示界面,选择设计文件的输入方式,例如Verilog HDLFile,则会打开输人编辑窗口,输入设计文件后,保存文件。

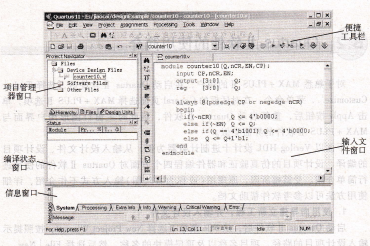

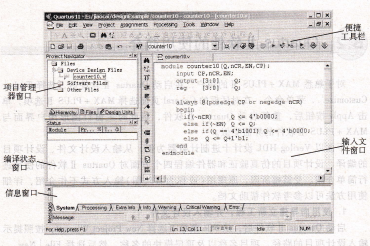

在上述操作完成后,出现图B.2.2所示的主窗口。窗口结构与一般Win~

dows中应用程序的窗口类似,主要由标题信息栏、主菜单栏、图标便捷工具栏、窗口主体以及底部的辅助信息提示栏组成。在窗口主体中,左边的是项目

图B.2,2 Quartus Ⅱ主窗口受篇幅所限,窗口中的菜单功能和使用方法可以参考软件帮助文档,此处不再赘述。

设计项目的编译,Quartus Ⅱ编译器主要完成设计项目的检查和逻辑综合,将项目的最终设成.

HDSP-431G上述工作完成后,由软件自动完成布局与布线工作,它以最优的方式对逻G件布局,并准确地完成元件之间的连线。

时序仿真使用包含延时信息的编译网表,不仅测试逻辑功能,还测试设计的逻辑在目标器件中最差情况下的时序关系,它和器件的实际工作情况基本一致,因此对整个设计项目进行时序仿真,分析其时序关系,评估设计的性能是非常必要的。

器件的编程与测试,在对设计的文件进行处理时,软件会自动产生供编程用的数据文件。对CPLD器件,编程文件为熔丝图文件;而对FPGA器件,编程文件为位流数据文件。对具有在系统编程功能的器件,可以使用相应的编程软件,通过编程电缆直接将编程数据写入到器件中。对没有在系统编程接口的器件,则需要使用专用编程器,才能对器件编程。对器件的编程完成后,需要对器件的功能进行

实际测试。

对于熟悉MAX+PLUS Ⅱ的用户,在启动Quartus Ⅱ软件后,选择Tods|Customize…菜单命令,在对话框的Genera1页面选择MAX+PLUS Ⅱ选项,单击Apply按钮后,重新启动Quartus Ⅱ软件,则此时主窗口图形用户界面与

MAX+PLUS Ⅱ软件的界面类似。

下面以Ⅴerilog HDL设计十进制计数器为例,从输入设计文件、设计项目的编译、设计项目的仿真验证和器件编程四个方面对Quartus Ⅱ软件的使用进行简单介绍。受篇幅所限,原理图(或称为方块图)输人方式不作介绍,详细使用方法可以参考软件帮助文档。

使用向导建立新工程,并输入设计文件,启动Quartus Ⅱ软件后,从Fne菜单下选择New Project Wizzard,按照提示输人设计项目的路径,项目名称以及顶层模块的名称。然后选择Fne|New...命令,出现图B.2.1所示界面,选择设计文件的输入方式,例如Verilog HDLFile,则会打开输人编辑窗口,输入设计文件后,保存文件。

在上述操作完成后,出现图B.2.2所示的主窗口。窗口结构与一般Win~

dows中应用程序的窗口类似,主要由标题信息栏、主菜单栏、图标便捷工具栏、窗口主体以及底部的辅助信息提示栏组成。在窗口主体中,左边的是项目

图B.2,2 Quartus Ⅱ主窗口受篇幅所限,窗口中的菜单功能和使用方法可以参考软件帮助文档,此处不再赘述。

设计项目的编译,Quartus Ⅱ编译器主要完成设计项目的检查和逻辑综合,将项目的最终设成.

公网安备44030402000607

公网安备44030402000607