VI-J5L-M 左右的滤波电容

发布时间:2019/10/24 12:28:27 访问次数:1785

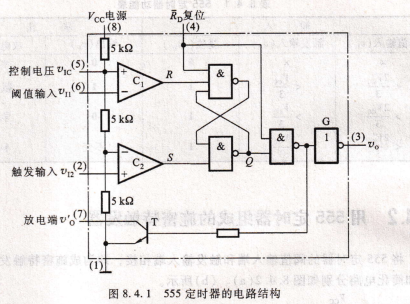

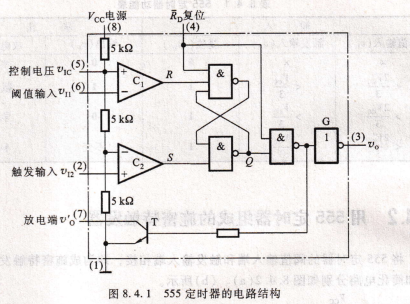

VI-J5L-M放电三极管T以及缓冲器G组成,其内部结构图如图8.4.1所示。三个5kΩ的电阻串联组成分压器,为比较器C1、C2提供参考电压。当控制电压端(5)悬空时(可对地接上0.01 uF左右的滤波电容),比较器C1和C2的基准电压分别为2/3VCC和vcc/3.

uI1是比较器C1的信号输入端 ,称为阈值输入端 ;vi2是比较器C2的信号输人端 ,称为触发输入端。如果控制电压端(5)外接电压vcc,则比较器C1、C2的基准电压就变为vic和寸。比较器C1和C2的输出控制SR锁存器和放电三极管T的态。

放电三极管T为外接电路提供放电通路 ,在使用定时器时 ,该三极管的集电极(7脚)一般都要外接上拉电阻。

RD为直接复位输人端 ,当RD为低电平时 ,不管其他输人端的状态如何,输出端v0即为低电平。

当uIl>2vcc/3,ui2>vcc/3时,比较器C1输出低电平 ,比较器C2输出高电平 ,简单SR锁存器0端置0,放电三极管T导通 ,输出端v0为低电平 。

当ui1<2vcc/3 ,ui2

用8K×8位RAM芯片构成32K×8位的存储器系统,实际应用中,常将两种方法相互结合,以达到字和位均扩展的要求。可见,无论需要多大容量的存储器系统,均可利用容量有限的存储器芯片,通过DRAM中存储的数据如果不进行周期性的刷新,其数据将会丢失;而SRAM中存储的数据无需刷新,只要电源不断电就可以永久保存,为什么?

一般情况下,DRAM的集成度比SRAM的集成度高,为什么?

sSRAM与异步SRAM的主要差别是什么?它有什么优点?

sSRAM中丛发模式读写操作的特点是什么?

用容量为16K×1位存储器芯片构成-一个32K×8位的存储系统,需要多少根地址线?多少根数据线?多少个16K×1位的存储器芯片?

与简单PLD(PAL、GAL等)相比,CPLD的集成度更高。CPLD具有更多的输入信号、更多的乘积项和更多的宏单元。尽管各厂商生产的CPLD器件结构

In system Programmabmy的缩写。

前面有关章节已介绍了可编程逻辑器件PAL和GAL,它们都属于简单的PLD。随着微电子技术的发展和应用上的需求,简单PLD在集成度和性能方面难以满足要求,因此集成度更高、功能更强的复杂可编程器件(CPLD)便迅速发展起来。早期的CPLD大多采用EPROM编程技术,其编程过程与简单PLD一样,每次编程需要在专用或通用设各上进行。后来采用E2PROM和闪烁存储器技术,使CPLD具有了“在系统可编程(ISP①)”特性。所谓在系统可编程是指未编程的ISP器件可以直接焊接在印制电路板上,然后通过计算机的数据传输端口和专用的编程电缆对焊接在电路板上的ISP器件直接多次编程,从而使器件具有所需要的逻辑功能。这种编程不需要使用专用的编程器,因为已将原来属于编程器的编程电路和升压电路集成在ISP器件内部。ISP技术使得调试过程不需要反复拔插芯片,从而不会产生引脚弯曲变形现象,提高了可靠性,而且可以随时对焊接在电路板上的ISP器件的逻辑功能进行修改,从而加快了数字系统的调试过程。目前,ISP已成为系统在线远程升级的技术手段。

VI-J5L-M放电三极管T以及缓冲器G组成,其内部结构图如图8.4.1所示。三个5kΩ的电阻串联组成分压器,为比较器C1、C2提供参考电压。当控制电压端(5)悬空时(可对地接上0.01 uF左右的滤波电容),比较器C1和C2的基准电压分别为2/3VCC和vcc/3.

uI1是比较器C1的信号输入端 ,称为阈值输入端 ;vi2是比较器C2的信号输人端 ,称为触发输入端。如果控制电压端(5)外接电压vcc,则比较器C1、C2的基准电压就变为vic和寸。比较器C1和C2的输出控制SR锁存器和放电三极管T的态。

放电三极管T为外接电路提供放电通路 ,在使用定时器时 ,该三极管的集电极(7脚)一般都要外接上拉电阻。

RD为直接复位输人端 ,当RD为低电平时 ,不管其他输人端的状态如何,输出端v0即为低电平。

当uIl>2vcc/3,ui2>vcc/3时,比较器C1输出低电平 ,比较器C2输出高电平 ,简单SR锁存器0端置0,放电三极管T导通 ,输出端v0为低电平 。

当ui1<2vcc/3 ,ui2

用8K×8位RAM芯片构成32K×8位的存储器系统,实际应用中,常将两种方法相互结合,以达到字和位均扩展的要求。可见,无论需要多大容量的存储器系统,均可利用容量有限的存储器芯片,通过DRAM中存储的数据如果不进行周期性的刷新,其数据将会丢失;而SRAM中存储的数据无需刷新,只要电源不断电就可以永久保存,为什么?

一般情况下,DRAM的集成度比SRAM的集成度高,为什么?

sSRAM与异步SRAM的主要差别是什么?它有什么优点?

sSRAM中丛发模式读写操作的特点是什么?

用容量为16K×1位存储器芯片构成-一个32K×8位的存储系统,需要多少根地址线?多少根数据线?多少个16K×1位的存储器芯片?

与简单PLD(PAL、GAL等)相比,CPLD的集成度更高。CPLD具有更多的输入信号、更多的乘积项和更多的宏单元。尽管各厂商生产的CPLD器件结构

In system Programmabmy的缩写。

前面有关章节已介绍了可编程逻辑器件PAL和GAL,它们都属于简单的PLD。随着微电子技术的发展和应用上的需求,简单PLD在集成度和性能方面难以满足要求,因此集成度更高、功能更强的复杂可编程器件(CPLD)便迅速发展起来。早期的CPLD大多采用EPROM编程技术,其编程过程与简单PLD一样,每次编程需要在专用或通用设各上进行。后来采用E2PROM和闪烁存储器技术,使CPLD具有了“在系统可编程(ISP①)”特性。所谓在系统可编程是指未编程的ISP器件可以直接焊接在印制电路板上,然后通过计算机的数据传输端口和专用的编程电缆对焊接在电路板上的ISP器件直接多次编程,从而使器件具有所需要的逻辑功能。这种编程不需要使用专用的编程器,因为已将原来属于编程器的编程电路和升压电路集成在ISP器件内部。ISP技术使得调试过程不需要反复拔插芯片,从而不会产生引脚弯曲变形现象,提高了可靠性,而且可以随时对焊接在电路板上的ISP器件的逻辑功能进行修改,从而加快了数字系统的调试过程。目前,ISP已成为系统在线远程升级的技术手段。

上一篇:ISL6140可编程乘积项阵列

公网安备44030402000607

公网安备44030402000607