FI-RE31S-HF 非阻塞型赋值

发布时间:2019/10/16 21:37:01 访问次数:3251

FI-RE31S-HF在always语句中对电平敏感事件和边沿敏感事件的描述有何不同?

阻塞型赋值和非阻塞型赋值有何区别?

试用verilog描述一个基本sR锁存器和一个下降沿触发的SR触发器。

锁存器和触发器都是具有存储功能的逻辑电路,是构成时序电路的基本逻辑单元。每个锁存器或触发器都能存储1位二值信息,所以又称为存储单元或记忆单元.

锁存器是对脉冲电平敏感的电路,它们在一定电平作用下改变状态。基本sR锁存器由输入信号电平直接控制其状态,传输门控或逻辑门控锁存器在使能电平作用下由输入信号决定其状态。在使能信号作用期间,门控锁存器输出跟随输入信号变化而变化。

触发器是对时钟脉冲边沿敏感的屯路,根据不同的电路结构,它们在时钟脉冲的上升沿或下降沿作用下改变状态。目前流行的触发器电路主要有主从、维持阻塞和利用传输延迟等几种结构,它们的工作原理各不相同。

触发器按逻辑功能分类有D触发器、JK触发器、T(r′)触发器和sR触发器。它们的功能可用特性表、特性方程和状态图来描述。触发器的电路结构与逻辑功能没有必然联系。例如JK触发器既有主从结构的,也有维持阻塞或利用传输延迟结构的。每一种逻辑功能的触发器都可以通过增加门电路和适当的外部连线转换为其他功能的触发器。

用verilog对锁存器与触发器做行为级描述,是描述时序电路的基础模块。

分析图例5.2.1所示电路的功能,列出功能表.

用cmos电路74HCT02或非构成消除机械开关抖动影响电路如图题5.2.2所示,试画出在开关S由位置A到B时Q和Q端的波形.如改用TTL电路74LS02实现,r1,r2取值的大致范围为多少?整个电路的功耗会发生什么变化.

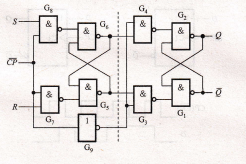

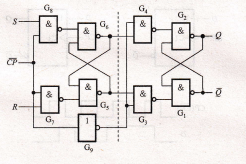

由与非或非门组成的SR锁存器如图题5.2.3所示,试分析其工作原理并列出功能表.

FI-RE31S-HF在always语句中对电平敏感事件和边沿敏感事件的描述有何不同?

阻塞型赋值和非阻塞型赋值有何区别?

试用verilog描述一个基本sR锁存器和一个下降沿触发的SR触发器。

锁存器和触发器都是具有存储功能的逻辑电路,是构成时序电路的基本逻辑单元。每个锁存器或触发器都能存储1位二值信息,所以又称为存储单元或记忆单元.

锁存器是对脉冲电平敏感的电路,它们在一定电平作用下改变状态。基本sR锁存器由输入信号电平直接控制其状态,传输门控或逻辑门控锁存器在使能电平作用下由输入信号决定其状态。在使能信号作用期间,门控锁存器输出跟随输入信号变化而变化。

触发器是对时钟脉冲边沿敏感的屯路,根据不同的电路结构,它们在时钟脉冲的上升沿或下降沿作用下改变状态。目前流行的触发器电路主要有主从、维持阻塞和利用传输延迟等几种结构,它们的工作原理各不相同。

触发器按逻辑功能分类有D触发器、JK触发器、T(r′)触发器和sR触发器。它们的功能可用特性表、特性方程和状态图来描述。触发器的电路结构与逻辑功能没有必然联系。例如JK触发器既有主从结构的,也有维持阻塞或利用传输延迟结构的。每一种逻辑功能的触发器都可以通过增加门电路和适当的外部连线转换为其他功能的触发器。

用verilog对锁存器与触发器做行为级描述,是描述时序电路的基础模块。

分析图例5.2.1所示电路的功能,列出功能表.

用cmos电路74HCT02或非构成消除机械开关抖动影响电路如图题5.2.2所示,试画出在开关S由位置A到B时Q和Q端的波形.如改用TTL电路74LS02实现,r1,r2取值的大致范围为多少?整个电路的功耗会发生什么变化.

由与非或非门组成的SR锁存器如图题5.2.3所示,试分析其工作原理并列出功能表.

公网安备44030402000607

公网安备44030402000607