eljre12njf2灵活处理的方法

发布时间:2019/10/18 23:49:51 访问次数:3076

eljre12njf2如果将图6.5.11所示电路中r触发器的激励方程组改为则可构成4位同步二进制减计数器,即每输人一个计数脉冲,计数器Q3、Q2、Ql、Q0的状态将按二进制编码值递减,读者可以自行列出状态表并分析其工作过程。

典型集成电路

74LⅤC161是一种典型的高性能、低功耗CMOS 4位同步二进制加计数器,它可在1,2~3.6Ⅴ电源电压范围内工作,其所有逻辑输人端都可耐受高达5.5V的电压,因此,在电源电压为3.3Ⅴ时可直接与5V供电的TTL逻辑电路接口。它的工作速度很高,从输人时钟脉冲CP上升沿到oⅣ输出的典型延迟时间仅3.9 ns,最高时钟工作频率可达200 MHz。

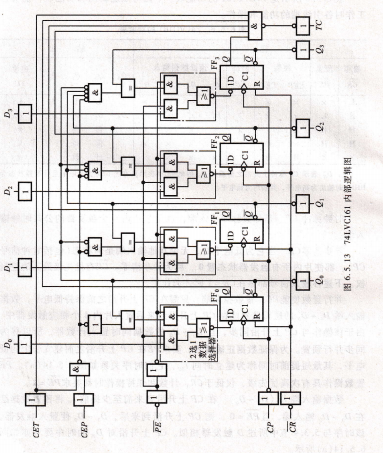

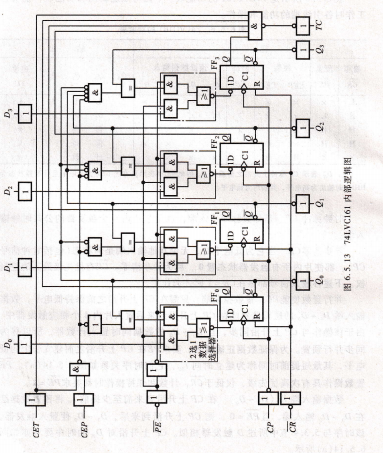

图6.5.13所示是74LVC161的内部逻辑图,除同步二进制计数功能外,电路还具有并行数据的同步预置功能。预置和计数功能的选择是通过在每个D触发器的输人端插入一个2选1数据选择器实现的。由于CMOs与或非门的电路结构比与或门更为简单,所以这里不像标准数据选择器那样用与一或结构实现,而是使用了与或非门构成2选1数据选择器。相应地,74LⅤC161中的D触发器也取D作为输入。这种灵活处理的方法在集成电路中是十分常见的。电路中,当PE=0时为并行数据预置操作,每个数据选择器左边的与门打开,于是,D3~D。到达相应触发器的输入端,当CP脉冲沿到达时,该组数据进入触发器而实现同步预置;当PE=1时,右边的与门打开,各D触发器与相应的同或门实现r触发器功能,接收同步计数的控制信号,其工作原理与图6.5.11所示电路相同。

eljre12njf2如果将图6.5.11所示电路中r触发器的激励方程组改为则可构成4位同步二进制减计数器,即每输人一个计数脉冲,计数器Q3、Q2、Ql、Q0的状态将按二进制编码值递减,读者可以自行列出状态表并分析其工作过程。

典型集成电路

74LⅤC161是一种典型的高性能、低功耗CMOS 4位同步二进制加计数器,它可在1,2~3.6Ⅴ电源电压范围内工作,其所有逻辑输人端都可耐受高达5.5V的电压,因此,在电源电压为3.3Ⅴ时可直接与5V供电的TTL逻辑电路接口。它的工作速度很高,从输人时钟脉冲CP上升沿到oⅣ输出的典型延迟时间仅3.9 ns,最高时钟工作频率可达200 MHz。

图6.5.13所示是74LVC161的内部逻辑图,除同步二进制计数功能外,电路还具有并行数据的同步预置功能。预置和计数功能的选择是通过在每个D触发器的输人端插入一个2选1数据选择器实现的。由于CMOs与或非门的电路结构比与或门更为简单,所以这里不像标准数据选择器那样用与一或结构实现,而是使用了与或非门构成2选1数据选择器。相应地,74LⅤC161中的D触发器也取D作为输入。这种灵活处理的方法在集成电路中是十分常见的。电路中,当PE=0时为并行数据预置操作,每个数据选择器左边的与门打开,于是,D3~D。到达相应触发器的输入端,当CP脉冲沿到达时,该组数据进入触发器而实现同步预置;当PE=1时,右边的与门打开,各D触发器与相应的同或门实现r触发器功能,接收同步计数的控制信号,其工作原理与图6.5.11所示电路相同。

公网安备44030402000607

公网安备44030402000607