MAX902EPD 时序电路的逻辑功能

发布时间:2019/10/8 12:15:18 访问次数:2148

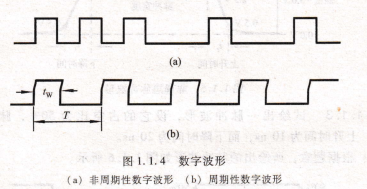

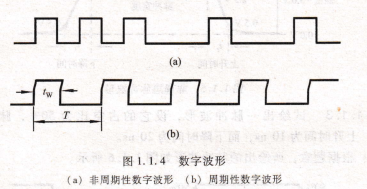

MAX902EPD图1.1.4 数字波形

(a)非周期性数字波形 (b)周期性数字波形

周期性数字波形常用周期r和频率r来描述。脉冲波形的脉冲宽度用fw表示,它表示脉冲的作用时间。另一个重要参数是占空比g,它表示脉冲宽度Tw占整个周期T的百分数,常用下式来表示

当占空比为50%时,称此时的矩形脉冲为方波,即0和1交替出现并持续占有相同的时间。

例1,1,2 设周期性数字波形的高电平持续6 ms,低电平持续10 ms,求占空比g。

解:因数字波形的脉冲宽度Jw=6 ms,周期r=(6+1o)ms=16 ms

g=甘%・三号飞×100% 375%

实际数字信号波形

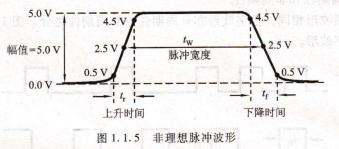

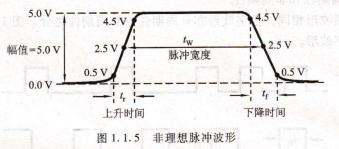

在实际的数字系统中,数字信号并没有那么理想。当它从低电平跳变到高电平,或从高电平跳到低电平时,边沿没有那么陡峭,而要经历一个过渡过程,分别用上升时间rr和下降时间莎r描述,如图1.1.5所示。将脉冲幅值的10%到90%时所经历的时间称为上升时间rr。下降时间则相反,从脉冲幅值的90%下降到10%时所经历的时间称为下降时间莎f。将脉冲幅值的50%的两个时间点所跨越的时间称为脉冲宽度Jw,对于不同类型的器件和电路,其上升和下降时间各不相同。一般数字信号上升和下降时间的典型值约为几纳秒(ns)。

图1,1.5 非理想脉冲波形

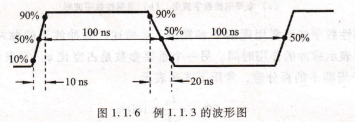

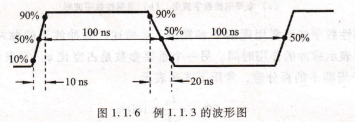

例1.1^3 试绘出一脉冲波形,设它的占空比为50%,脉冲宽度为100 ns,上升时间为10 ns,而下降时间为20 ns。

解:根据题意,所绘出的脉冲波形如图1.1.6所示。

图1.1.6 例1.1.3的波形图

本书所用的数字波形大多数将画成理想波形。实际上,每一波形均有上升时间和下降时间。由于rr和Jf与脉冲宽度的时间相比非常小,则不必在每一波形上表示出来。画波形的目的只是为了知道高、低电平所经历的时间。

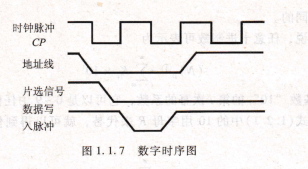

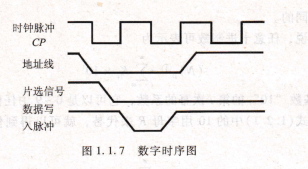

时序图,在数字电路中,常用时序图或称为脉冲波形图,来分析时序电路的逻辑功能。表明各信号之间时序关系的波形图称为时序图。图1,1.7所示为一典型的时序图。图中CP为时钟脉冲信号,它是数字系统中的时间参考信号。地址线、片选和数据写入等信号亦示于图1.1.7中。关于时序图中各个波形的具体作用,将在后续章节中介绍。通常数字集成电路,例如存储器和时序逻辑器件等均须附有时序图,以便于进行数字系统的分析、设计和应用。

MAX902EPD图1.1.4 数字波形

(a)非周期性数字波形 (b)周期性数字波形

周期性数字波形常用周期r和频率r来描述。脉冲波形的脉冲宽度用fw表示,它表示脉冲的作用时间。另一个重要参数是占空比g,它表示脉冲宽度Tw占整个周期T的百分数,常用下式来表示

当占空比为50%时,称此时的矩形脉冲为方波,即0和1交替出现并持续占有相同的时间。

例1,1,2 设周期性数字波形的高电平持续6 ms,低电平持续10 ms,求占空比g。

解:因数字波形的脉冲宽度Jw=6 ms,周期r=(6+1o)ms=16 ms

g=甘%・三号飞×100% 375%

实际数字信号波形

在实际的数字系统中,数字信号并没有那么理想。当它从低电平跳变到高电平,或从高电平跳到低电平时,边沿没有那么陡峭,而要经历一个过渡过程,分别用上升时间rr和下降时间莎r描述,如图1.1.5所示。将脉冲幅值的10%到90%时所经历的时间称为上升时间rr。下降时间则相反,从脉冲幅值的90%下降到10%时所经历的时间称为下降时间莎f。将脉冲幅值的50%的两个时间点所跨越的时间称为脉冲宽度Jw,对于不同类型的器件和电路,其上升和下降时间各不相同。一般数字信号上升和下降时间的典型值约为几纳秒(ns)。

图1,1.5 非理想脉冲波形

例1.1^3 试绘出一脉冲波形,设它的占空比为50%,脉冲宽度为100 ns,上升时间为10 ns,而下降时间为20 ns。

解:根据题意,所绘出的脉冲波形如图1.1.6所示。

图1.1.6 例1.1.3的波形图

本书所用的数字波形大多数将画成理想波形。实际上,每一波形均有上升时间和下降时间。由于rr和Jf与脉冲宽度的时间相比非常小,则不必在每一波形上表示出来。画波形的目的只是为了知道高、低电平所经历的时间。

时序图,在数字电路中,常用时序图或称为脉冲波形图,来分析时序电路的逻辑功能。表明各信号之间时序关系的波形图称为时序图。图1,1.7所示为一典型的时序图。图中CP为时钟脉冲信号,它是数字系统中的时间参考信号。地址线、片选和数据写入等信号亦示于图1.1.7中。关于时序图中各个波形的具体作用,将在后续章节中介绍。通常数字集成电路,例如存储器和时序逻辑器件等均须附有时序图,以便于进行数字系统的分析、设计和应用。

公网安备44030402000607

公网安备44030402000607