拨码开关保护电路原理

发布时间:2019/1/11 20:42:02 访问次数:2529

【处理措施】JA3515-OS-A04

(1)利用静电放电干扰信号就近泄放的特点,改变金属面板的开孔面积,同时适当增大拨码开关与面板之间的距离,使在静电放电操作时,静电放电枪头与拨码开关的距离〃2始终大于静电放电枪头与金属面板的距离Ⅱ1,放电不会发生在静电放电枪头与拨码开关之间。

(2)拨码开关中受到静电放电袭击的信号线上加瞬态抑制器件或抑制电路,抑制静电放电产生的高电压和过电流。

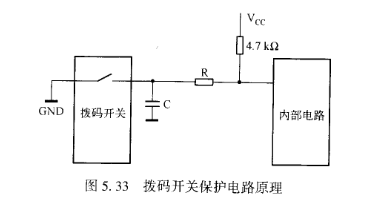

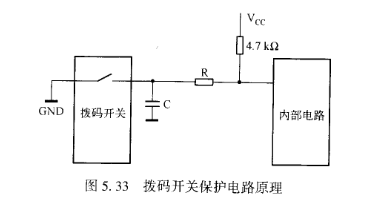

产品中由于受开发时间的限制,最终采用的是在拨码开关的电路上增加保护电路的方式,拨码开关与内部电路之间的ESD保护电路原理如图5.33所示。

图533 拨码开关保护电路原理

电路中电容的取值在1000pF~0.0I uF之间,用来滤除静电放电时产生的高电压;串接一个约50Ω的电阻R(ESD要求较高时也可用TⅤS代替图中的电容,推荐的TVS如PSOT05)用来抑制静电放电时产生的过电流。测试证明此电路可以使该产品通过空气放电±I5kⅤ测试。

【思考与启示】

(1)类似产品设计时,要考虑图5.32中所提到的〃1、〃2之间的关系,应使凡始终大于〃1,或达到放电距离时。

(2)易受静电放电干扰的电路有必要增加瞬态抑制电路或滤波电路。

【处理措施】JA3515-OS-A04

(1)利用静电放电干扰信号就近泄放的特点,改变金属面板的开孔面积,同时适当增大拨码开关与面板之间的距离,使在静电放电操作时,静电放电枪头与拨码开关的距离〃2始终大于静电放电枪头与金属面板的距离Ⅱ1,放电不会发生在静电放电枪头与拨码开关之间。

(2)拨码开关中受到静电放电袭击的信号线上加瞬态抑制器件或抑制电路,抑制静电放电产生的高电压和过电流。

产品中由于受开发时间的限制,最终采用的是在拨码开关的电路上增加保护电路的方式,拨码开关与内部电路之间的ESD保护电路原理如图5.33所示。

图533 拨码开关保护电路原理

电路中电容的取值在1000pF~0.0I uF之间,用来滤除静电放电时产生的高电压;串接一个约50Ω的电阻R(ESD要求较高时也可用TⅤS代替图中的电容,推荐的TVS如PSOT05)用来抑制静电放电时产生的过电流。测试证明此电路可以使该产品通过空气放电±I5kⅤ测试。

【思考与启示】

(1)类似产品设计时,要考虑图5.32中所提到的〃1、〃2之间的关系,应使凡始终大于〃1,或达到放电距离时。

(2)易受静电放电干扰的电路有必要增加瞬态抑制电路或滤波电路。

上一篇:ESD与敏感信号的电容旁路

公网安备44030402000607

公网安备44030402000607