多测试结构的Wafer示意图

发布时间:2017/11/19 17:19:58 访问次数:1625

yield定义的扩展:对于MPW(multiple product wafer)的wafer而言,在同一套光罩(mask)上,可以摆放不同的产品。如图17.2所示,一套光罩上有a、b、c种不同的产品。 HCF4556M013TR浅色代表测试通过,深色代表测试未通过,那么以产品划分计算”eld时a、b、c的yield分别是50%、75%、75%。

如果把它们作为一个整体,那么reticlc yield就是25%(在一个reticle中,任何一个die失效都将定义为整个reticle的失效)。

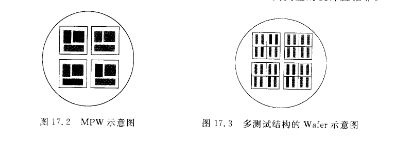

对于非产品的test chip,在一个chip内往往有多个测试结构(Device Under Tcst,DUT)。由于设计和分析上的考虑,往往需要根据DUT的特征分组计算”eld。如图17,3所示,在一个die里有四组DUT,每组是两个同类型的设计且相邻。 若不对这些DUT做任何的区分,可以得到struct urc”cld为78,l%(32个DUT中有

7个失效),而die”eld为25%(1/4,仅右上die没有失效)。若仅考察每个die左下的一组DUT,那么,structure yield为75%(每个die有两个

structure,共8个,其中2个失效),dic yield为50%(2/4,左上,右下的两个die失效)。

yield定义的扩展:对于MPW(multiple product wafer)的wafer而言,在同一套光罩(mask)上,可以摆放不同的产品。如图17.2所示,一套光罩上有a、b、c种不同的产品。 HCF4556M013TR浅色代表测试通过,深色代表测试未通过,那么以产品划分计算”eld时a、b、c的yield分别是50%、75%、75%。

如果把它们作为一个整体,那么reticlc yield就是25%(在一个reticle中,任何一个die失效都将定义为整个reticle的失效)。

对于非产品的test chip,在一个chip内往往有多个测试结构(Device Under Tcst,DUT)。由于设计和分析上的考虑,往往需要根据DUT的特征分组计算”eld。如图17,3所示,在一个die里有四组DUT,每组是两个同类型的设计且相邻。 若不对这些DUT做任何的区分,可以得到struct urc”cld为78,l%(32个DUT中有

7个失效),而die”eld为25%(1/4,仅右上die没有失效)。若仅考察每个die左下的一组DUT,那么,structure yield为75%(每个die有两个

structure,共8个,其中2个失效),dic yield为50%(2/4,左上,右下的两个die失效)。

上一篇:yield的基本定义及扩展

上一篇:缺陷密度与良率模型

热门点击

热门点击

- 曝光能量宽裕度,归一化图像对数斜率(NILs

- CVD是用来制备二氧化硅介质薄膜的主要工艺方

- 中频电压与直流电压比值大

- 退火过程中晶粒的变化

- 光刻胶配制原理

- 进行剂量补偿是刻蚀后检查(AEI)CDU改善

- 有机物、金属、颗粒的去除(SC1):

- 正向阻断峰值电压

- PODEM算法是由Goel等人提出的

- 光刻技术发展历史

推荐技术资料

推荐技术资料

- 业余条件下PCM2702

- PGM2702采用SSOP28封装,引脚小而密,EP3... [详细]

公网安备44030402000607

公网安备44030402000607