薄膜质量控制

发布时间:2017/5/18 21:25:25 访问次数:1621

薄膜质量,主要是指薄膜是否为保形覆盖,界面应力类型与大小,薄膜的致密性、厚度均ON4986匀性、附着性等几方面特性。通过分析薄膜的质量特性,对淀积过程进行控制,从而制备出满足微电子I艺所需的薄膜。

台阶覆盖特性

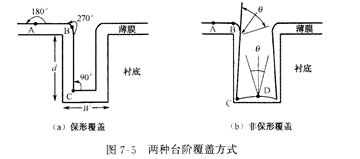

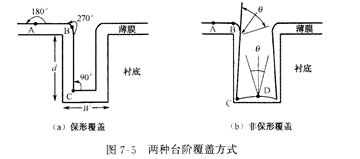

在制备薄膜之前,通常在衬底上已经进行了多个单项工艺操作,衬底表面不再是平面,而是存在台阶。而随着超大规模集成电路集成度的不断提高,单元结构尺寸已进入了深亚微米级,造成衬底表面微结构的深宽比也越来越大,因此,薄膜的台阶覆盖性能成为淀积薄膜质量控制的关键问题。淀积薄膜会出现如图75所示的两种台阶覆盖方式:保形覆盖和非保形覆盖。保形覆盖是指无论衬底表面有什么样的微结构图形,在上面淀积的薄膜都有相同的厚度。集成电路工艺中多数情况下希望淀积薄膜是保形覆盖。

保形覆盖是由同一衬底不同位置薄膜淀积速率是否均匀一致决定的。由7.2,2节分析可知C、0薄膜淀积速率主要由衬底温度和表面反应剂浓度决定。同一衬底不同位置的温度可以看成是完全相同的,当衬底温度升高时,衬底表面吸附的反应剂和表面反应生成的原子或分子在衬底表面迁移率就会提高,使得在同一衬底不同位置的分布趋于均匀,淀积的薄膜厚度就会趋于均匀。而表面反应剂浓度的影响较为复杂。反应剂分子(或原子团)是通过气相扩散穿过边界层到达衬底表面的,所以表面反应剂的浓度与同一衬底不同位置的到达角及边界层厚度有关。

薄膜质量,主要是指薄膜是否为保形覆盖,界面应力类型与大小,薄膜的致密性、厚度均ON4986匀性、附着性等几方面特性。通过分析薄膜的质量特性,对淀积过程进行控制,从而制备出满足微电子I艺所需的薄膜。

台阶覆盖特性

在制备薄膜之前,通常在衬底上已经进行了多个单项工艺操作,衬底表面不再是平面,而是存在台阶。而随着超大规模集成电路集成度的不断提高,单元结构尺寸已进入了深亚微米级,造成衬底表面微结构的深宽比也越来越大,因此,薄膜的台阶覆盖性能成为淀积薄膜质量控制的关键问题。淀积薄膜会出现如图75所示的两种台阶覆盖方式:保形覆盖和非保形覆盖。保形覆盖是指无论衬底表面有什么样的微结构图形,在上面淀积的薄膜都有相同的厚度。集成电路工艺中多数情况下希望淀积薄膜是保形覆盖。

保形覆盖是由同一衬底不同位置薄膜淀积速率是否均匀一致决定的。由7.2,2节分析可知C、0薄膜淀积速率主要由衬底温度和表面反应剂浓度决定。同一衬底不同位置的温度可以看成是完全相同的,当衬底温度升高时,衬底表面吸附的反应剂和表面反应生成的原子或分子在衬底表面迁移率就会提高,使得在同一衬底不同位置的分布趋于均匀,淀积的薄膜厚度就会趋于均匀。而表面反应剂浓度的影响较为复杂。反应剂分子(或原子团)是通过气相扩散穿过边界层到达衬底表面的,所以表面反应剂的浓度与同一衬底不同位置的到达角及边界层厚度有关。

公网安备44030402000607

公网安备44030402000607